# Optimierung von Networks-on-Chip mit Hilfe der dynamischen Rekonfiguration

Dem Fachbereich Elektrotechnik, Informationstechnik, Medientechnik der Bergischen Universität Wuppertal zur Erlangung des akademischen Grades eines Doktor-Ingenieurs genehmigte Dissertation

von

M. Sc. -Ing. Alexander Logvinenko

Wuppertal, den 08. September 2014

Die Dissertation kann wie folgt zitiert werden:

#### Kurzfassung

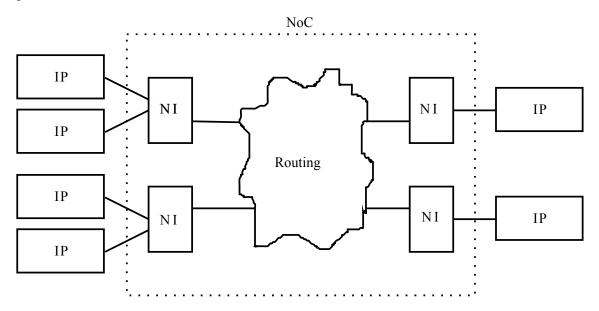

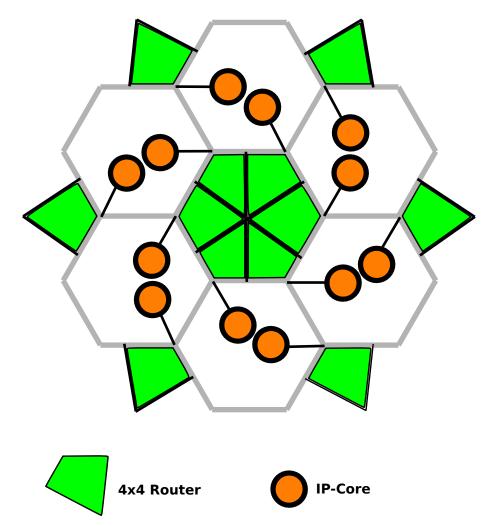

Moderne Prozessoren werden modular entwickelt. Dadurch muss bei Neuentwicklungen nicht alles neu geplant werden, sondern es kann auf bereits vorgefertigte Komponenten – sogenannte IP Blocks (Intellectual Property Blocks) – zurückgegriffen werden.

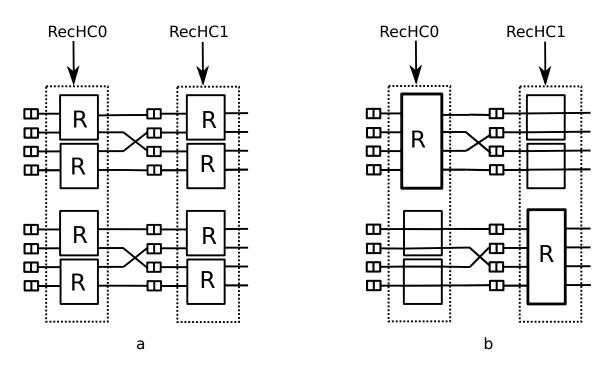

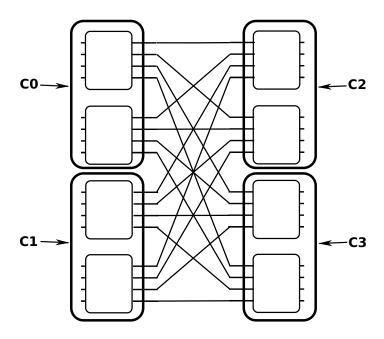

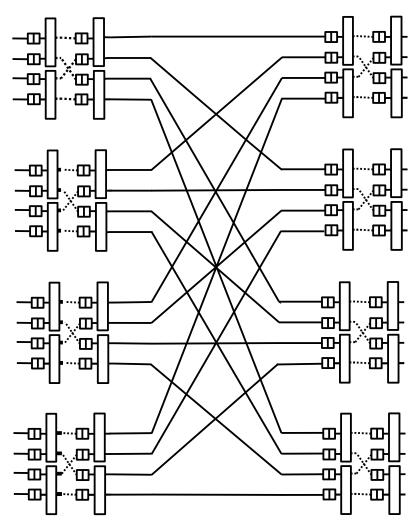

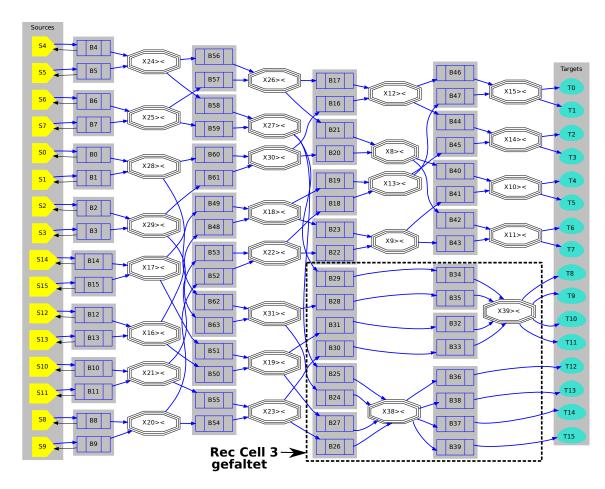

Um die einzelnen IPs miteinander verbinden zu können, wurde eine rekonfigurationsfähige Architektur für Network-on-Chip entwickelt: Reconfigurable Multi-Interconnection Network (RecMIN). Diese ist in der Lage, sich an die aktuelle Datenverkehrssituation des Netzes anzupassen.

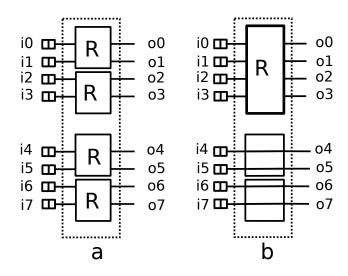

Die entwickelte Architektur besteht aus einzelnen rekonfigurierbaren Zellen. Zusätzlich weist die Rekonfigurationsarchitektur einen höheren Wiederverwendungsgrad für die Hardware-Strukturen auf, z.B. bzgl. Puffer, Multiplexer. Das bedeutet, dass die Komponenten der alten Topologie auch nach der Rekonfiguration für die neue Topologie aktiv verwendet werden.

Um die Simulation der Rekonfigurationsarchitektur zu ermöglichen, wurde ein Simulationsporgramm RecSim implementiert.

Zum Schluss werden drei Algorithmen präsentiert, die das Verhalten des RecMIN beobachten und bei Bedarf eine Rekonfiguration durchführen. Auf diese Weise soll die Netztopologie auch bei Belastungsänderungen optimal an den Datenverkehr angepasst bleiben.

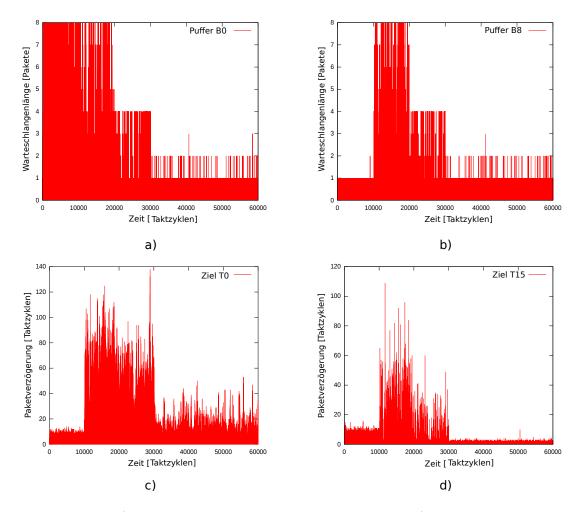

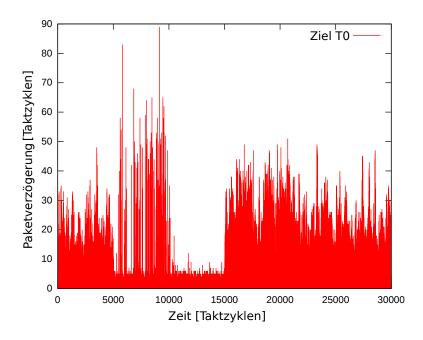

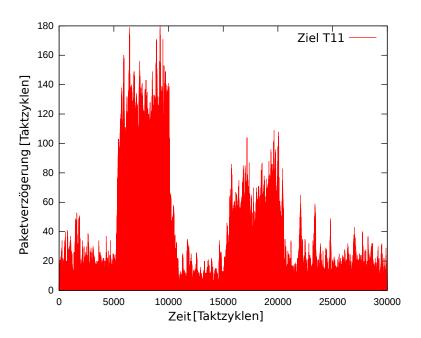

Die Ergebnisse der Simulation haben gezeigt, dass die hier vorgeschlagene rekonfigurierbare Netzwerkstruktur das Potential hat, die Leistungsfähigkeit einiger Anwendungen, insbesondere derer, die zwischen zwei oder mehreren Verkehrsprofilen wechseln, drastisch zu verbessern. So, z. B., würde diese Baustruktur die Paketverzögerungen bedeutend (bis zu Faktor sieben) reduzieren (s. Kapitel 6).

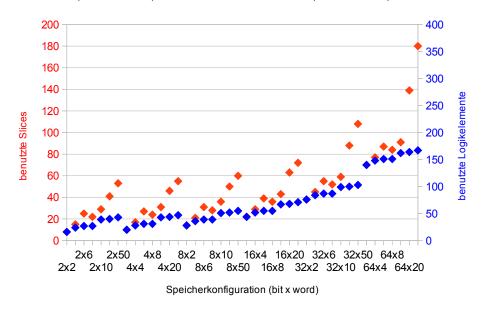

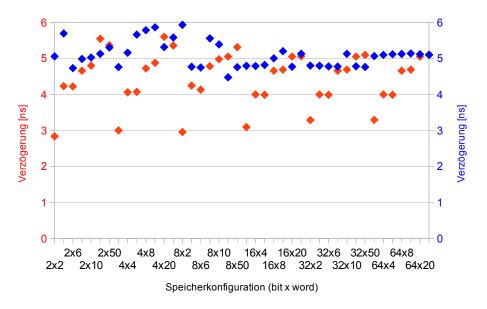

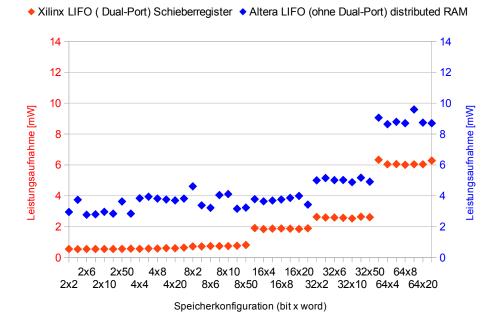

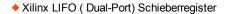

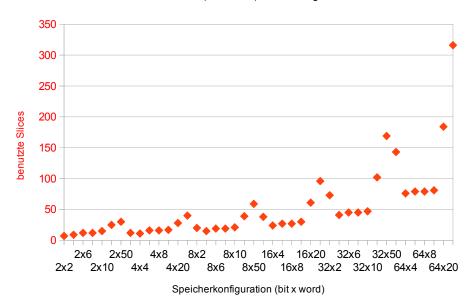

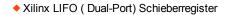

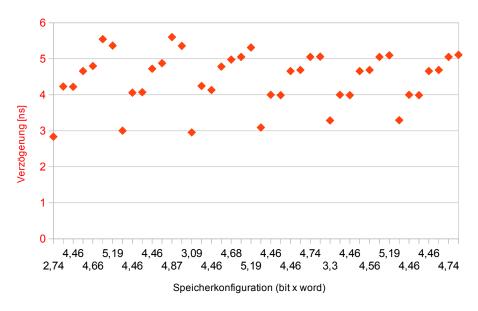

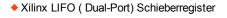

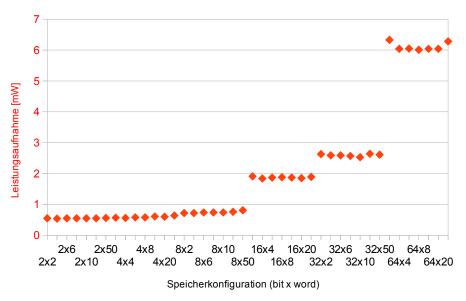

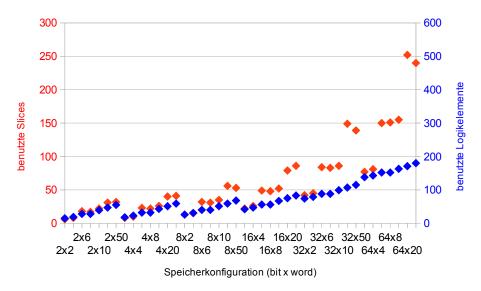

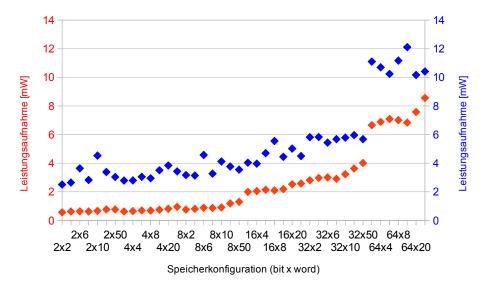

Für die Hardwarerealisierung der RecMIN-Architektur auf FPGA ist Xilinx-FPGA mit FIFO-Speicherprinzip (beim einfachen FIFO für die RecMINs mit dünnem Paketverkehr) als eine der besten Lösungen zu empfehlen. Wird aber für RecMIN ein Ringspeicher gewählt, was vor allem für einen starken Paketverkehr sinnvoll ist, so wäre die Wahl zwischen Altera- und Xilinx-FPGAs für jeden konkreten Fall mithilfe der Daten aus den Abbildungen 7.9 - 7.11 individuell zu treffen.

Der Vergleich zwischen den drei vorgeschlagenen Rekonfigurationsalgorithmen liefert folgende Schlussfolgerungen:

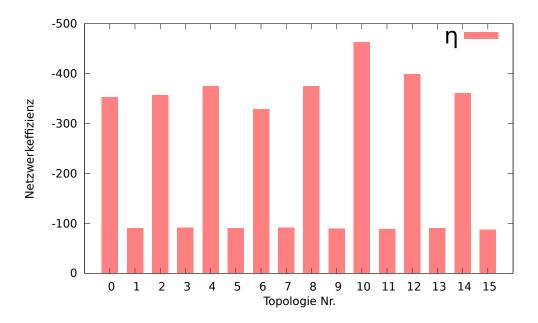

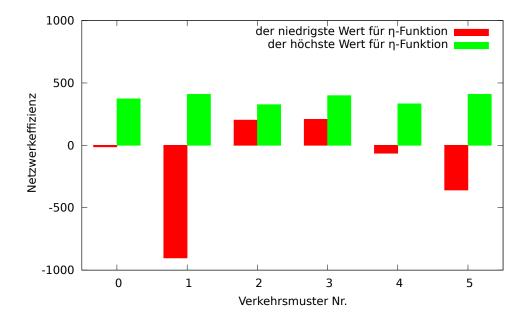

Der  $\eta$ -Algorithmus kann in Computersimulationen verwendet werden, um die von anderen Algorithmen (die keine erschöpfende Suche benutzen) erzielten Ergebnisse zu vergleichen. Jedoch ist das Integrieren des  $\eta$ -Algorithmus in ein SoC mit großem Hardware-Aufwand verbunden.

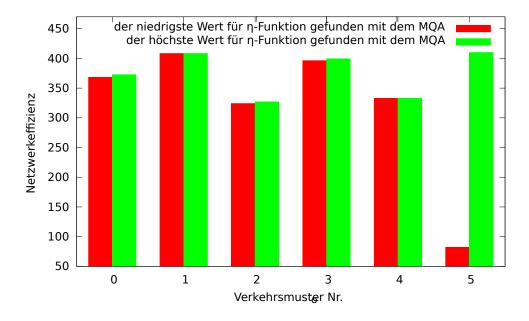

Der Minimal-Queues-Algorithmus (MQA) ist schneller als der  $\eta$ -Algorithmus und erfordert weniger Fläche auf dem Chip. Er kann mit kleinerem Hardware-Aufwand als der  $\eta$ -Algorithmus in SoC integriert werden. Der MQA ist dann zu empfehlen,

falls die Vorkenntnisse über die Eigenschaften des möglichen Verkehrs im Netzwerk nicht vorhanden sind.

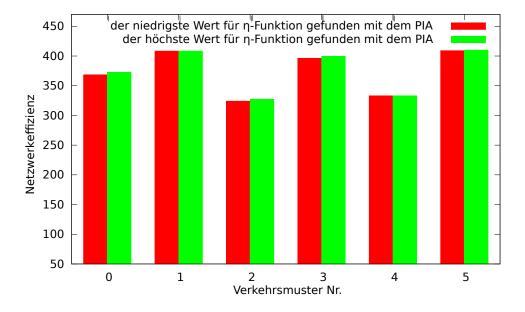

Der Pattern-Identification-Algorithmus (PIA) ist in den meisten Fällen schneller als der  $\eta$ -Algorithmus und der Minimal-Queues-Algorithmus. Die Umsetzung des PIAs auf SoC ist relativ einfach. Im Falle, dass die Muster für den PIA optimal implementiert sind, ist der PIA von allen drei hier für RecMIN vorgeschlagenen Reconfigurationsalgorithmen die effizienteste Lösung.

#### **Abstract**

Modern processors are developed modularly. Therefore new developments need not be re-scheduled from the scratch; rather prefabricated components – so-called IP blocks (Intellectual Property blocks) – can be used.

In order to connect the individual IPs, a reconfigurable architecture for network-on-chip has been developed: Reconfigurable Multi-Interconnection Network (RecMIN). It is able to adapt to the current traffic situation of the network.

The developed architecture consists of single reconfigurable cells. In addition, the reconfiguration architecture has a higher degree of reuse for the hardware structures, such as regarding buffer, multiplexer. This means that the components of the previously active topology are actively used also after the reconfiguration to the new topology.

In order to enable the simulation of the reconfiguration architecture, a simulation program RecSim was implemented.

Finally, three algorithms are presented that observe the behavior of the RecMIN and perform a reconfiguration when needed. In this way the network topology is to remain optimally adapted to the traffic even if the load changes.

The results of the simulation showed that the proposed reconfigurable network structure has the potential to improve the performance of some applications, especially those which switch between two or more traffic profiles. For some applications RecMIN-architecture would significantly reduce paket delays (up to factor seven) (see chapter 6).

For the hardware realization of the RecMIN-architecture on FPGA a Xilinx-FPGA with FIFO-buffer concept is recommended, as one of the best solutions for the RecMin realization. However, if circular buffer is chosen for RecMIN, which mostly makes sense for high packet traffic, the choice between Altera- and Xilinx-FPGAs would have to be made individually, for each specific case, based on the data from the images 7.9 – 7.11.

The comparison between the three suggested reconfiguration algorithms provides the following conclusion:

$\eta$ -algorithm can be used in computer simulations to compare the results achieved from other algorithms However, integrating the  $\eta$ -algorithm into a SoC is attended with hardware complexity.

Minimal-Queues-Algorithm (MQA) is faster than the  $\eta$ -algorithm and requires less area on the SoC. It can be integrated into SoC with less hardware complexity than  $\eta$ -algorithm. The MQA is a best solution in case that foreknowledge about the nerwork traffic are not available.

The Pattern-Identification-Algorithm (PIA) is faster than the  $\eta$ -algorithm and the Minimal-Queue-Algorithm. In case of properly implementation of the pattern for the PIA, the PIA is the most efficient of three algorithms proposed in this work.

## Inhaltsverzeichnis

| Τ | Einleitung                              |                                                                     |    |  |

|---|-----------------------------------------|---------------------------------------------------------------------|----|--|

|   | 1.1                                     | Motivation                                                          | 1  |  |

|   | 1.2                                     | Beitrag und Einordnung                                              | S  |  |

|   | 1.3                                     | Aufbau                                                              | 4  |  |

| 2 | NoC im Vergleich zu Off-Chip Netzwerken |                                                                     | 6  |  |

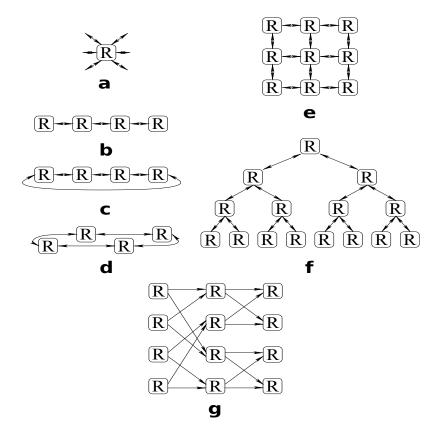

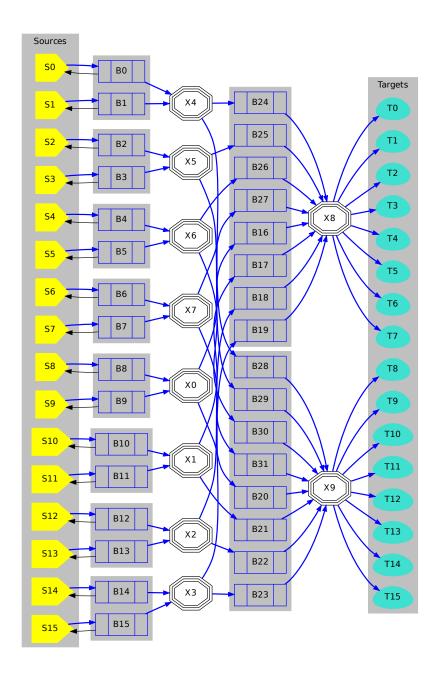

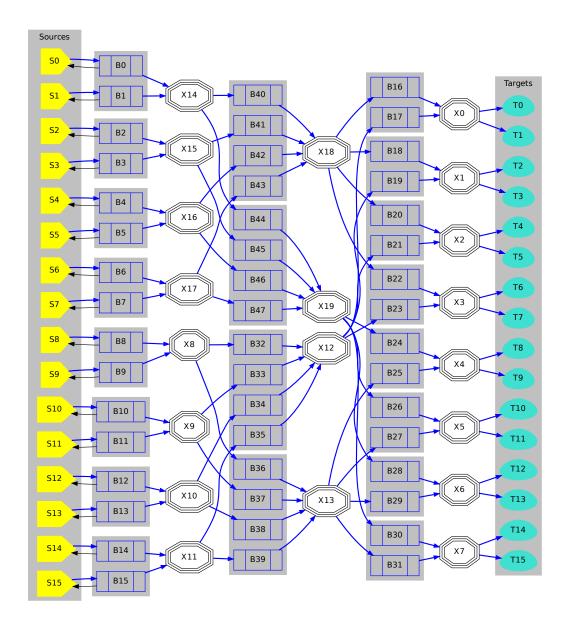

|   | 2.1                                     | Network-on-Chip                                                     | 7  |  |

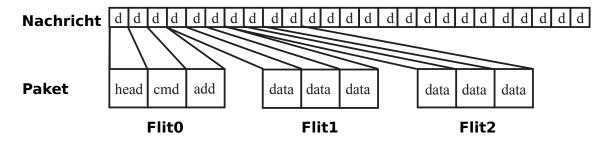

|   | 2.2                                     | Paketbasierter Verkehr                                              | Ĉ  |  |

|   | 2.3                                     | Vermittlungsart des Pakettransfers                                  | 10 |  |

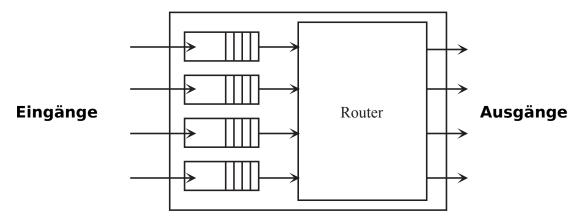

|   | 2.4                                     | Router                                                              | 10 |  |

|   | 2.5                                     | Vorgehensweise von Warteschlangen                                   | 11 |  |

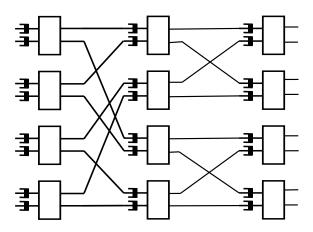

|   | 2.6                                     | Struktur und die Funktionsweise des Multistage-Interconnection Net- |    |  |

|   |                                         | work                                                                | 14 |  |

|   | 2.7                                     | Network on Chip und Rekonfiguration                                 | 16 |  |

| 3 | Rek                                     | Rekonfigurationstechniken 1                                         |    |  |

|   | 3.1                                     | Einleitung                                                          | 18 |  |

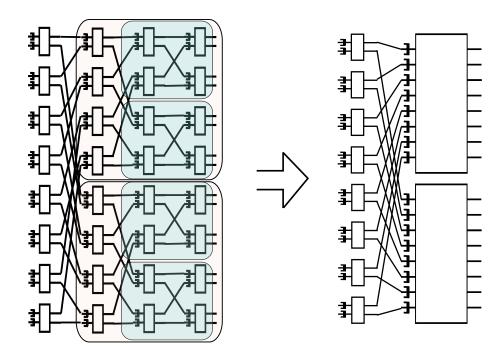

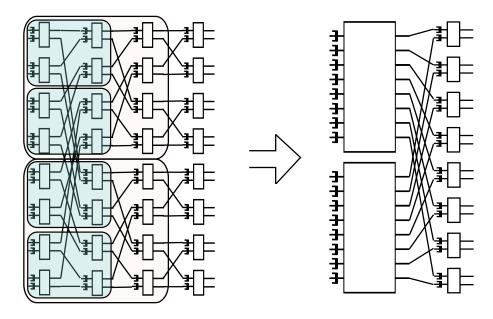

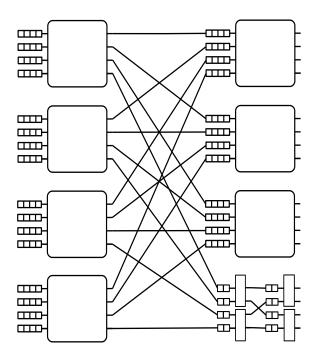

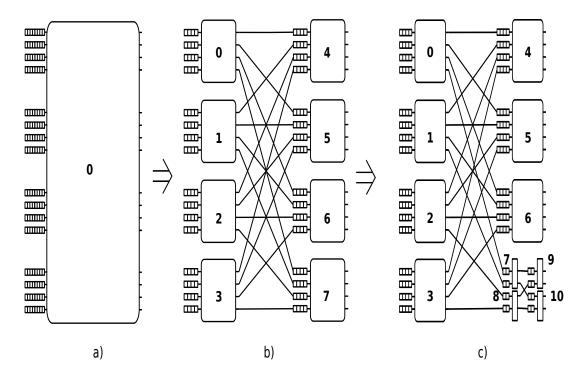

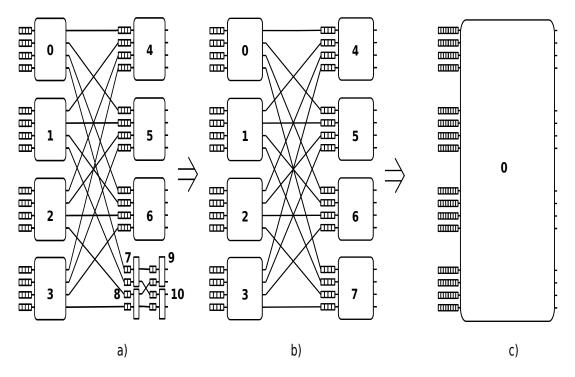

|   | 3.2                                     | Algorithmus des Netzwerkzerfalls und Synthese                       | 20 |  |

|   | 3.3                                     | Diskussion des Alpha+ und Alpha- Zerfalls                           | 24 |  |

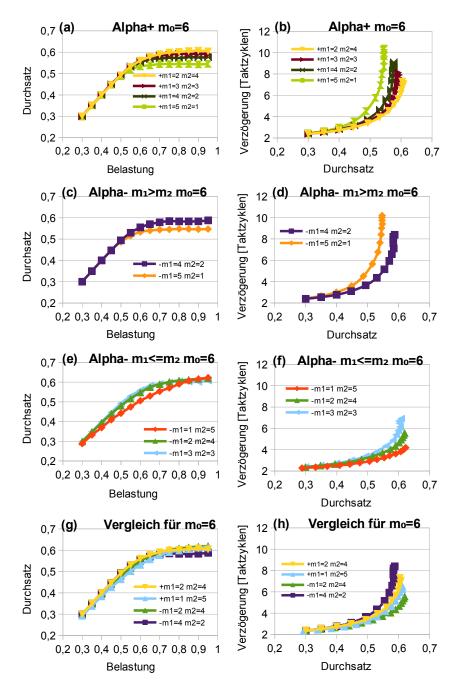

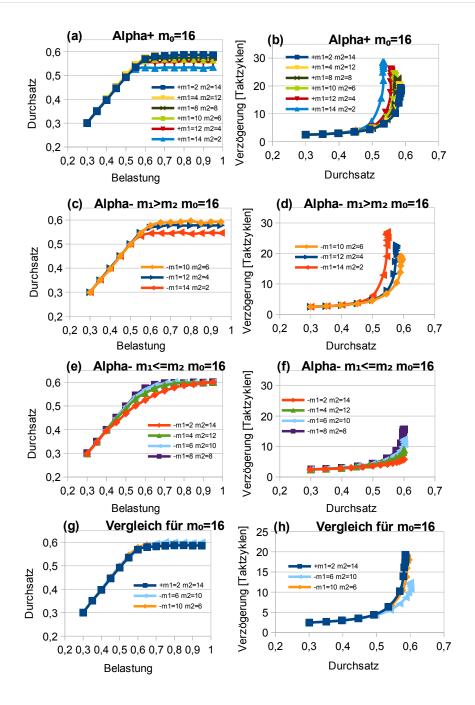

|   | 3.4                                     | Ergebnisse der Rekonfiguration                                      | 25 |  |

| 4 | Net                                     | Netzwerkberechnung 30                                               |    |  |

|   | 4.1                                     | Stand der Forschung                                                 | 30 |  |

|   | 4.2                                     | Das analytische Modell für einen einzelnen Router mit unendlichen   |    |  |

|   |                                         | Eingangs-Warteschlangen und begrenzer Pufferlänge                   | 32 |  |

|   | 4.3                                     | Ein Versuch der Modellerweiterung auf die symmetrischen-MIN Struk-  |    |  |

|   |                                         | turen                                                               | 34 |  |

| 5 | Simulator-Tool RecSim 38                |                                                                     |    |  |

|   | 5.1                                     | Einleitung                                                          | 38 |  |

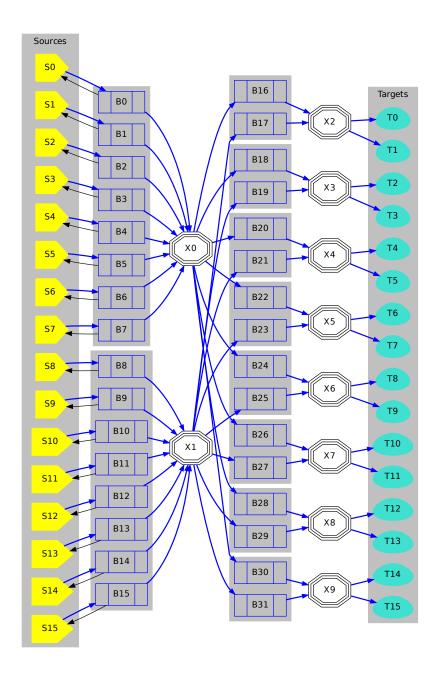

|   | 5.2                                     | Komponentenbasiertes Verbindungsnetz in $RecSim$                    | 39 |  |

|   | 5.3                                     | Generierung von $2^k$ -MIN                                          |    |  |

|   | 5.4                                     | Simulation und Rekonfiguration                                      | 46 |  |

|   | 5.5                                     | Ergehnisse                                                          | 48 |  |

| 6 |                                       | onfigurierbare Netzwerk-Architektur RecMIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55   |  |

|---|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

|   | 6.1                                   | Allgemein                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |  |

|   | 6.2                                   | Rekonfiguration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |  |

|   | 6.3                                   | Ergebnisse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 59 |  |

| 7 | Untersuchung der Hardwarerealisierung |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |  |

|   | 7.1                                   | Einführung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |  |

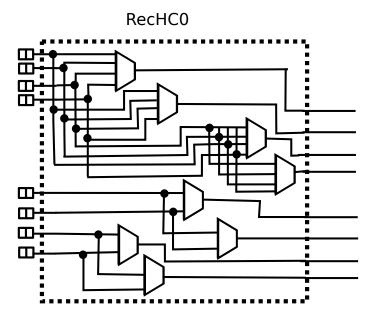

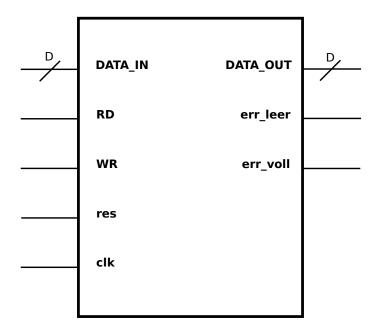

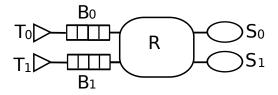

|   | 7.2                                   | Entwurf der Entity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |  |

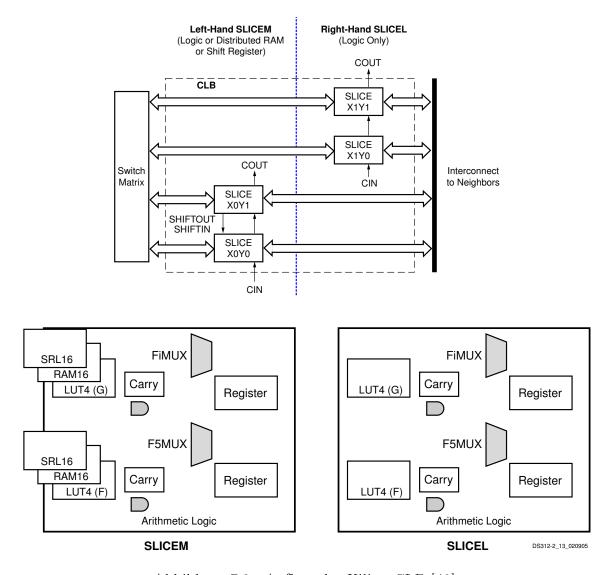

|   | 7.3                                   | Die Verwendeten FPGA-Architekturen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |  |

|   | 7.4                                   | Organisation der Basiszellen bei EP2C15- und XC3S500E-FPGAs $% \left( 1\right) =\left( 1\right) +\left( 1\right)$ |      |  |

|   | 7.5                                   | Eingebettete Speicher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |  |

|   | 7.6                                   | Ergebnisgewinnung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |  |

|   | 7.7                                   | Leistungsaufnahme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |  |

|   | 7.8                                   | Speichererkennung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |  |

|   | 7.9                                   | IP-Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |  |

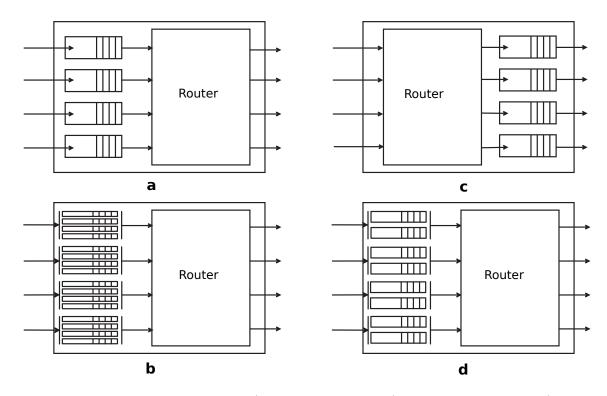

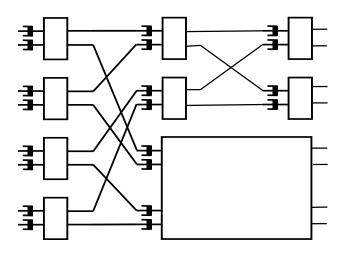

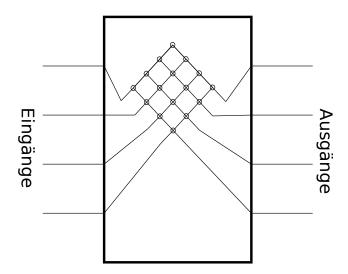

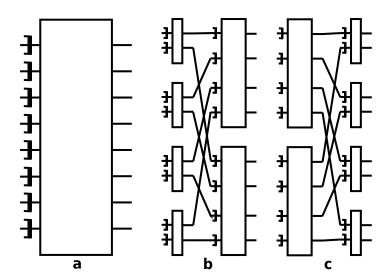

|   | 7.10                                  | Vergleiche und Ergebnisse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |  |