# FACHBEREICH MATHEMATIK UND NATURWISSENSCHAFTEN BERGISCHE UNIVERSITÄT WUPPERTAL

Entwicklung eines strahlenharten Controllers für das Kontrollsystem des ATLAS-Pixeldetektors am HL-LHC

Dissertation von Jennifer Boek Diese Dissertation kann wie folgt zitiert werden:

urn:nbn:de:hbz:468-20130305-093136-4

[http://nbn-resolving.de/urn/resolver.pl?urn=urn:nbn:de:hbz:468-20130305-093136-4]

# Inhaltsverzeichnis

| 1 | Ein  | leitung                                                                     | 1  |

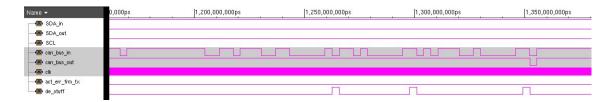

|---|------|-----------------------------------------------------------------------------|----|

| 2 | Die  | Luminositätssteigerung des LHC                                              | 9  |

|   | 2.1  | Das Standardmodell der Elementarteilchenphysik                              | 4  |

|   | 2.2  | Das Higgs-Boson                                                             | 7  |

|   | 2.3  | Physikalische Messungen am HL-LHC                                           | 11 |

|   | 2.4  | Das Upgrade des LHC zum HL-LHC                                              | 13 |

|   | 2.5  | Der ATLAS-Detektor für den HL-LHC                                           | 14 |

|   | 2.6  | Der ATLAS-Pixeldetektor für den HL-LHC                                      | 18 |

|   |      | 2.6.1 Die End-Of-Stave-Karte                                                | 21 |

| 3 | Das  | Kontrollsystem für den zukünftigen ATLAS-Pixeldetektor                      | 23 |

|   | 3.1  | Anforderungen an das Detektorkontrollsystem                                 | 24 |

|   | 3.2  | Aufbau des zukünftigen DCS                                                  | 25 |

|   |      | 3.2.1 Der DCS-Chip                                                          | 28 |

|   |      | 3.2.2 DCS-Konzepte für zwei unterschiedliche Ansätze der Detektorversorgung | 30 |

|   | 3.3  | Der DCS-Controller-Chip                                                     | 33 |

|   | 3.4  | Vergleich der Leitungsanzahl des momentanen und des zukünftigen DCS         | 35 |

| 4 | Stra | ahlenschäden in digitalen integrierten Schaltungen                          | 39 |

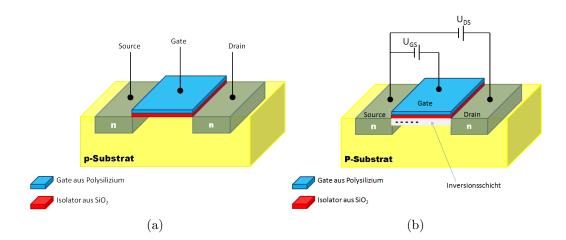

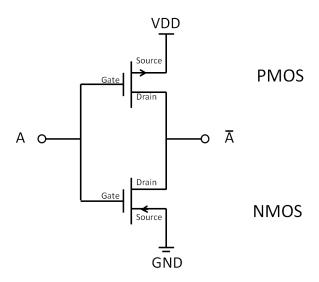

|   | 4.1  | Aufbau einer digitalen integrierten Schaltung                               | 39 |

|   | 4.2  | Schädigung durch Teilchenstrahlen                                           | 41 |

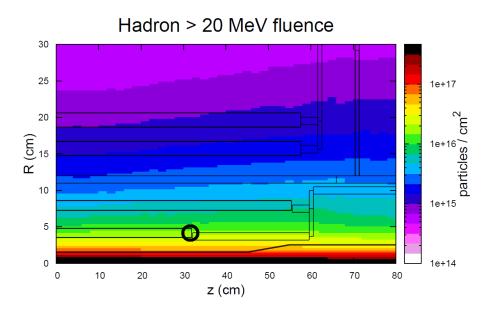

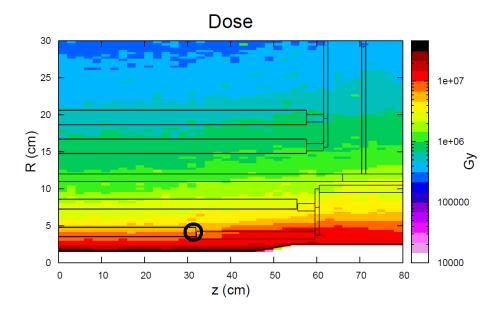

|   |      | 4.2.1 Erwartete Strahlungsumgebung für den HL-LHC                           | 41 |

|   |     | 4.2.2    | Betrachtung von Schädigungen durch Einzelfehlereffekte $$               | 43 |

|---|-----|----------|-------------------------------------------------------------------------|----|

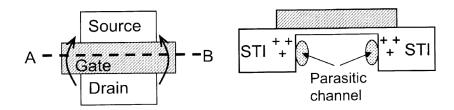

|   |     | 4.2.3    | Ionisationseffekte in CMOS-Komponenten                                  | 46 |

|   | 4.3 | Absch    | ätzung der Strahlentoleranz des 130 nm Prozesses                        | 47 |

| 5 | Die | Suche    | nach einer geeigneten DCS-Kommunikation                                 | 49 |

|   | 5.1 | Castin   | ıg                                                                      | 50 |

|   | 5.2 | Das I2   | C-HC-Protokoll                                                          | 52 |

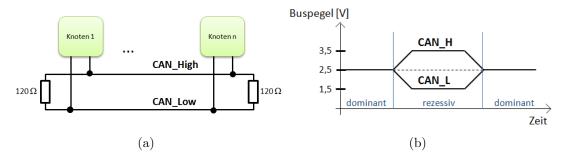

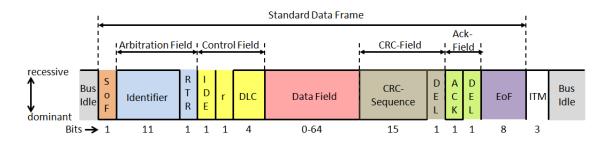

|   | 5.3 | Die G    | rundlagen des CAN-Protokolls                                            | 54 |

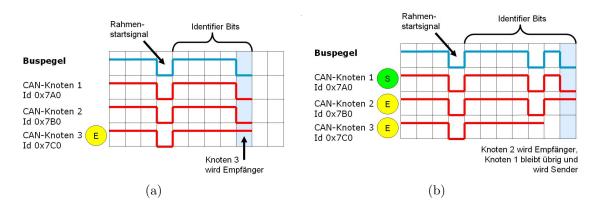

|   |     | 5.3.1    | Die bitweise Arbitrierung                                               | 56 |

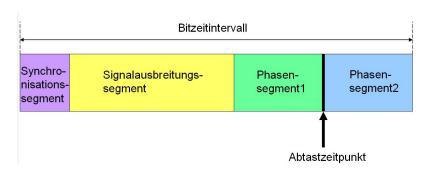

|   |     | 5.3.2    | Die Synchronisation der CAN-Bus-Teilnehmer                              | 57 |

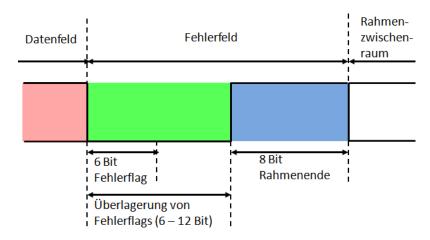

|   |     | 5.3.3    | Fehlererkennungsmechanismen im CAN-Protokoll                            | 58 |

|   | 5.4 | Die er   | wartete Fehlerrate für die DCS-Kommunikation                            | 60 |

| 6 | Dig | itales ( | Chipdesign für das Detektorkontrollsystem                               | 63 |

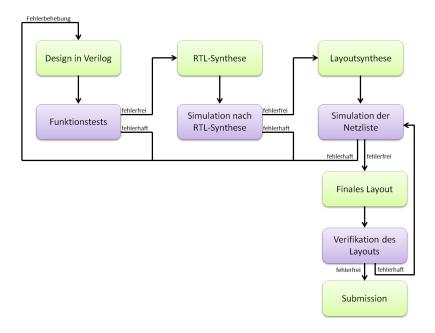

|   | 6.1 | Der di   | gitale Entwurfsprozess                                                  | 63 |

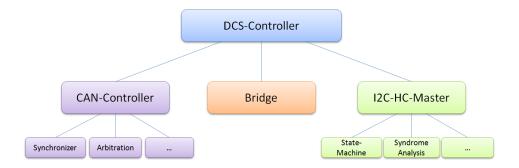

|   | 6.2 | Strukt   | ur der entwickelten Programme für den DCS-Controller $$                 | 65 |

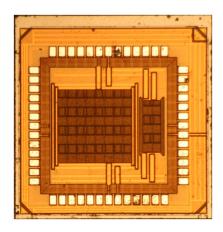

|   | 6.3 | Der er   | ste Prototyp-Chip für den DCS-Controller                                | 69 |

|   | 6.4 | Entwi    | cklung eines weiteren Prototypen für den DCS-Controller                 | 73 |

|   |     | 6.4.1    | Überarbeitung der Kommunikationsprotokolle $\ \ldots \ \ldots \ \ldots$ | 73 |

|   |     | 6.4.2    | Neue Befehlsstruktur und zusätzliche Funktionen                         | 77 |

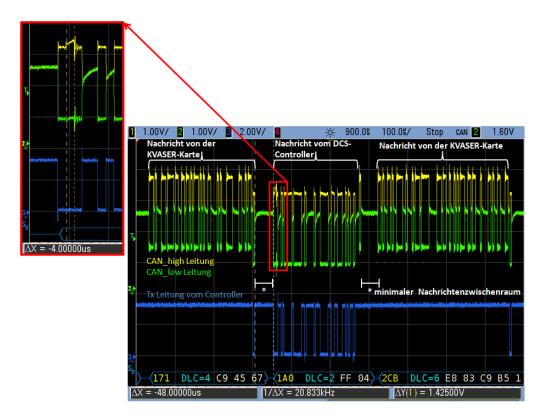

|   |     | 6.4.3    | Funktionstests                                                          | 80 |

|   |     | 6.4.4    | Laufzeitsimulationen des Designs für den DCS-Controller                 | 84 |

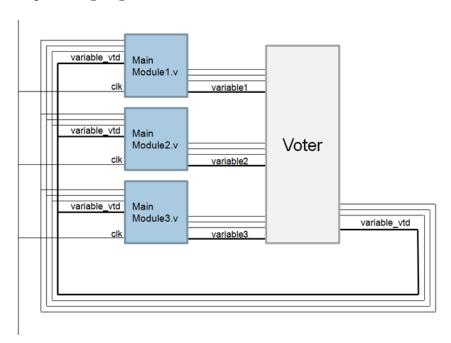

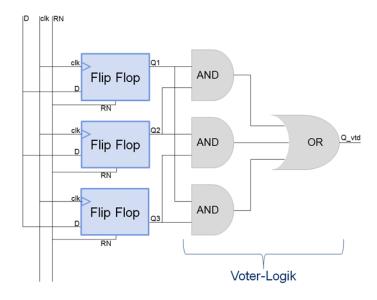

|   |     | 6.4.5    | Absicherung der Datenspeicherung gegen SEU                              | 85 |

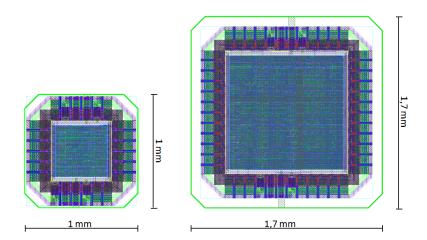

|   |     | 6.4.6    | Submission zweier Designs für SEU-Studien                               | 86 |

|   | 6.5 | Übersi   | icht der Prototypen im 130 nm Prozess für das DCS                       | 87 |

| 7 | Auf | bau de   | es Control und Feedback Pfades                                          | 89 |

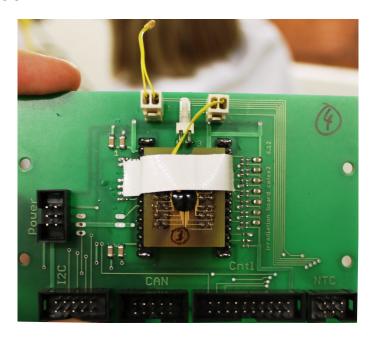

|   | 7.1 | Der zv   | veite Prototyp des DCS-Controllers                                      | 89 |

|   |     | 7.1.1    | Probleme mit CoFee2_TMR                                                 | 90 |

|   |     | 7.1.2    | Funktionalität des CoFee2_noTMR                                         | 90 |

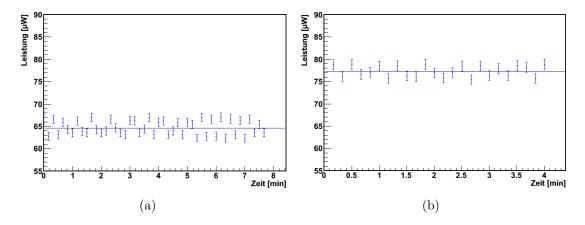

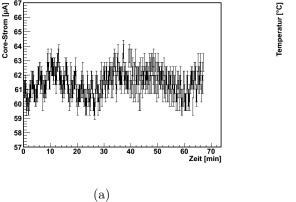

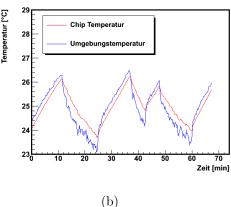

|   | 7.2 | Leistu   | ngsverbrauch des DCS-Controllers                                        | 92 |

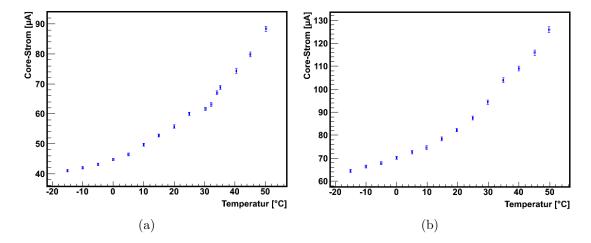

|   |     | 7.2.1    | Die Temperaturabhängigkeit des Core-Stroms                              | 94 |

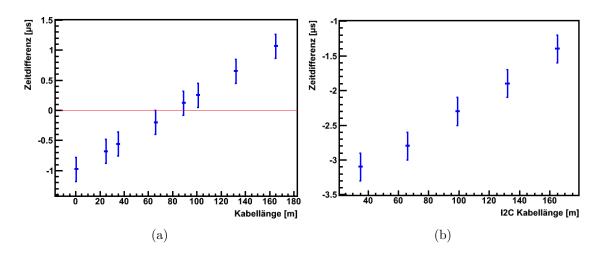

|   | 7.3 | Die Re   | eichweite der I2C-HC-Kommunikation                                      | 95 |

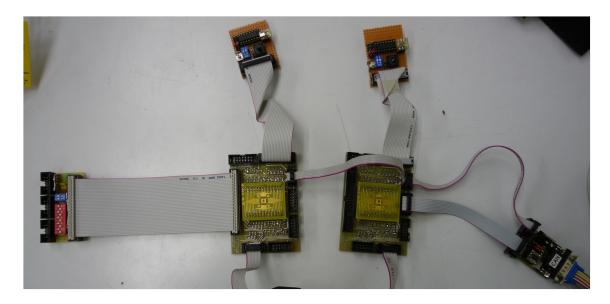

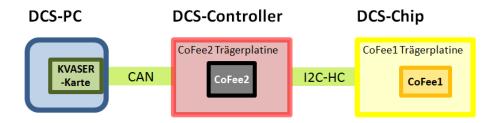

|              | 7.4   | Aufbau eines DCS-Netzwerks aus den vorhandenen Prototypen      | 96  |

|--------------|-------|----------------------------------------------------------------|-----|

|              | 7.5   | Zusammenfassung                                                | 97  |

| 8            | Me    | ssung der SEU-Fehlerrate des DCS-Chips                         | 99  |

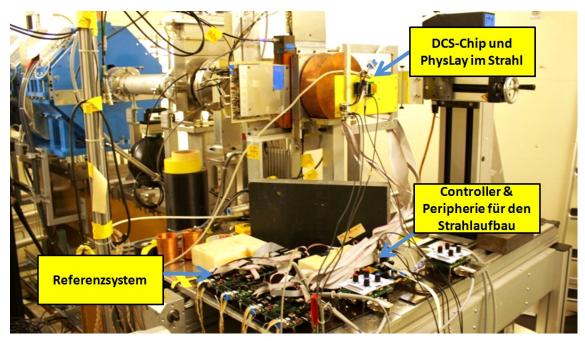

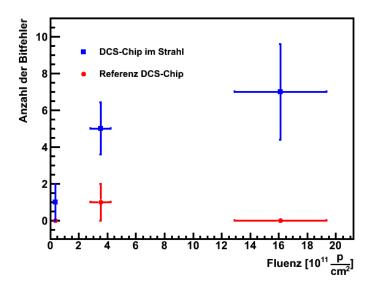

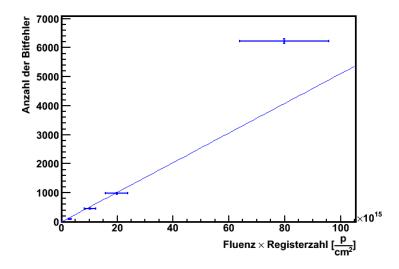

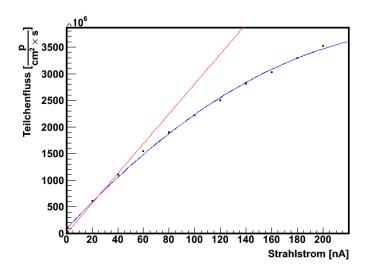

|              | 8.1   | Das Bestrahlungsprogramm                                       | 100 |

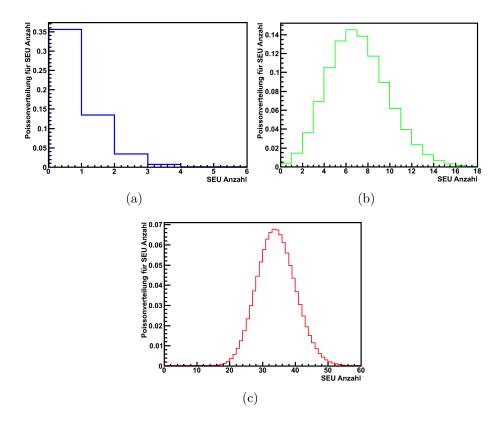

|              | 8.2   | Wirkungsquerschnitt für SEU des DCS-Chips                      | 103 |

|              | 8.3   | Verhalten der TMR-abgesicherten I2C-HC-Kommunikation im Strahl | 108 |

|              | 8.4   | Leistungsverbrauch des DCS Chips                               | 110 |

|              | 8.5   | Zusammenfassung                                                | 113 |

| 9            | Val   | idierung der Kommunikation zum Detektor unter Bestrahlung      | 115 |

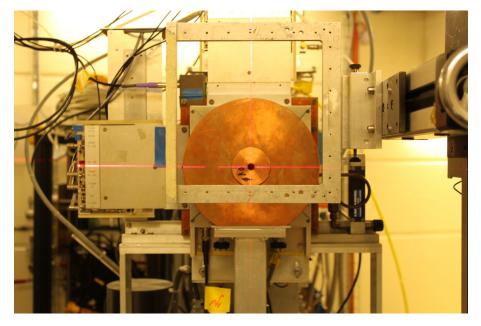

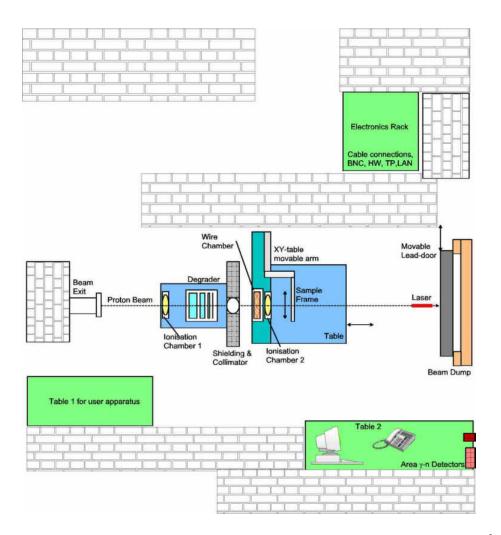

|              | 9.1   | Das Bestrahlungsprogramm                                       | 115 |

|              | 9.2   | Bestimmung des SEU-Wirkungsquerschnitts                        | 119 |

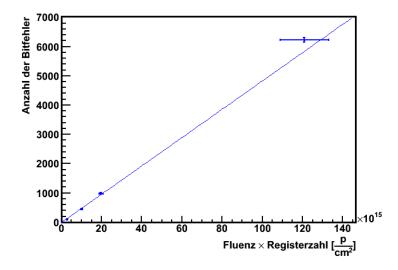

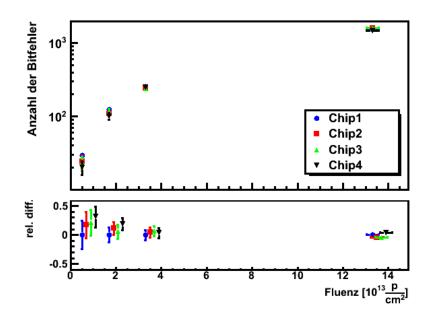

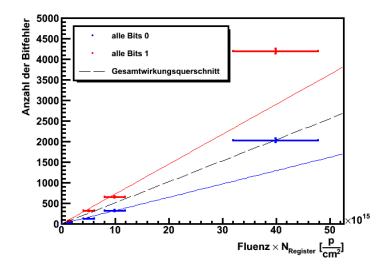

|              |       | 9.2.1 Bestimmung des SEU-Wirkungsquerschnitts                  | 120 |

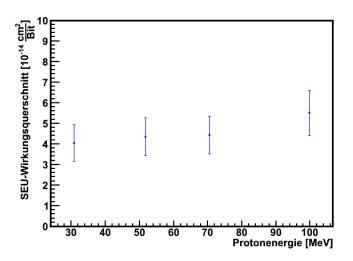

|              |       | 9.2.2 Energieabhängigkeit des SEU-Wirkungsquerschnitts         | 125 |

|              | 9.3   | Bestimmung der Strahlenhärte der CAN-Kommunikation             | 125 |

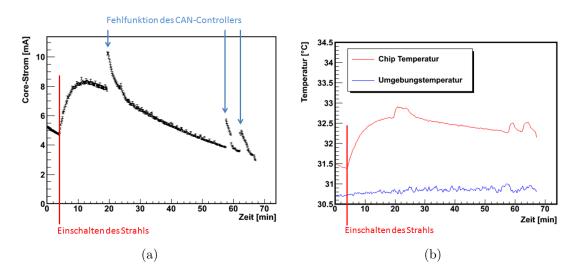

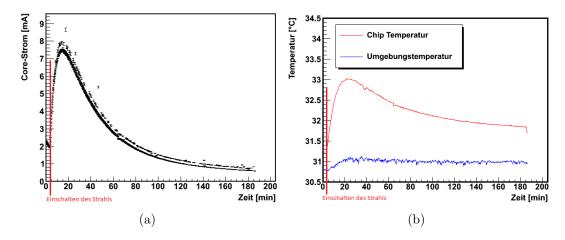

|              | 9.4   | Dosiseffekte am Beispiel des DCS-Controller-Prototypen         | 130 |

|              |       | 9.4.1 Weitere Studien                                          | 133 |

|              | 9.5   | Zusammenfassung                                                | 135 |

| 10           | Erg   | ebnisse und Ausblick                                           | 137 |

| Qı           | uelle | nverzeichnis                                                   | 139 |

| $\mathbf{A}$ | bild  | lungsverzeichnis                                               | 142 |

| Ta           | bell  | enverzeichnis                                                  | 146 |

# Kapitel 1

# **Einleitung**

Der weltweit größte Protonenbeschleuniger, der Large Hadron Collider (= LHC) am CERN, ist seit 2009 in Betrieb. Bei Schwerpunktsenergien von bis zu  $\sqrt{s}=8\,\mathrm{TeV}$  nehmen die Experimente Daten auf. Ein grundlegender Erfolg ist die Entdeckung eines neuen Bosons durch die Experimente ATLAS und CMS.

Das Upgrade des LHC zum High Luminosity Large Hadron Collider (= HL-LHC) gilt der Suche nach neuer Physik bis zu sehr hohen Teilchen-Massen. Aufgrund der erhöhten Luminosität können die physikalischen Prozesse mit einer besseren Statistik vermessen werden. Davon profitieren auch die physikalischen Studien des neu entdeckten Bosons, das noch eindeutig als das Higgs-Boson identifiziert werden muss.

Die Luminositätserhöhung zum HL-LHC stellt die Detektorentwicklung vor eine Herausforderung, da sich die zu erwartenden Teilchenraten stark vergrößern werden. Eine Konsequenz daraus ist der komplette Neubau des ATLAS-Spurdetektors, speziell des ATLAS-Pixeldetektors, der in Kapitel 2 ausführlicher beschrieben wird.

Da der ATLAS-Pixeldetektor komplett neu gebaut wird, werden viele grundlegende Komponenten verändert. Aus diesem Grund muss ein neues Detektorkontrollsystem (= DCS) für den zukünftigen Pixeldetektor aufgebaut werden. Die Anforderungen und der Aufbau des zukünftigen DCS werden in Kapitel 3 vorgestellt. Aus dem Konzept für das zukünftige Detektorkontrollsystem geht hervor, dass Chipdesign für die DCS-Komponenten nötig wird, um eine sichere, strahlenharte und möglichst Material reduzierte DCS-Kommunikation zum Detektor aufzubauen.

Im Rahmen dieser Arbeit wurde ein digitales Chipdesign erstellt, das eine Controller Area Network Kommunikation (= CAN-Kommunikation) beinhaltet. Diese Komponente wird DCS-Controller genannt und gewährleistet zusammen mit dem DCS-Chip die sichere DCS-Datenübertragung für jeden Betriebsmodus des Pixeldetektors.

Für ein besseres Verständnis der zu erwarteten Strahlenschädigung der DCS-Komponenten im 130 nm Prozess, werden in Kapitel 4 sowohl Einzelfehlereffekte, als auch Dosiseffekte diskutiert.

In Kapitel 5 wird ein geeignetes Datenprotokoll für die DCS-Kommunikation bestimmt, das später in dem DCS-Controller implementiert wird.

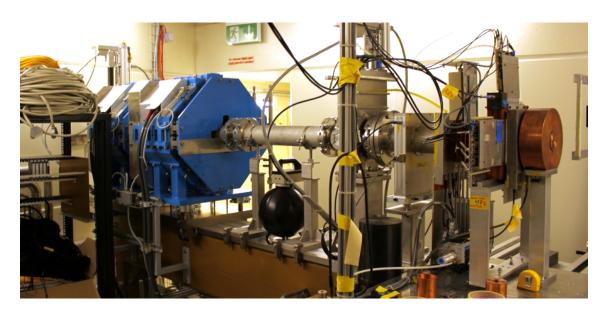

Neben der Entwicklung des DCS-Controllers (Kapitel 6) und der Verifikation der Funktionsfähigkeit (in Kapitel 7) wurden Messungen mit einem Protonenstrahl am Paul Scherrer Institut in der Schweiz durchgeführt, die bestätigen, dass die fehlerfreie Datenübertragung auch in der erwarteten Strahlungsumgebung für den HL-LHC gegeben ist (vgl. Kapitel 8 und 9).

# Kapitel 2

# Die Luminositätssteigerung des LHC

Die Luminosität ist das Maß für die Wahrscheinlichkeit von Protonzusammenstößen in den kollidierenden Strahlen eines Ringbeschleunigers. Sie trifft eine Aussage über die Leistungsfähigkeit des Beschleunigers. Die Luminosität für Teilchenbeschleuniger ist [1]:

$$L = \frac{n \cdot N_1 \cdot N_2 \cdot f}{A} \tag{2.1}$$

$N_1$  und  $N_2$  stehen für die Anzahl der Teilchen in den kollidierenden Strahlen mit der Anzahl von n Paketen. Der Parameter f ist die Kollisionsfrequenz und A die effektive Querschnittsfläche der Teilchenpakete im Wechselwirkungspunkt.

Die integrierte Luminosität  $\mathcal{L}$  gibt die über einen bestimmten Zeitraum  $\Delta T$  addierte Luminosität an:

$$\mathcal{L} = \int_{\Delta T} L \cdot dt \tag{2.2}$$

Die Einheit der integrierten Luminosität ist die invertierte Fläche und wird in inversen barn (b) angegeben. Dabei entspricht  $1\,\mathrm{b^{-1}} = 10^{24}\,\mathrm{cm^{-2}} = 10^{28}\,\mathrm{m^{-2}}.$

Die Anzahl der produzierten Ereignisse  $N_x$  eines bestimmten Prozesses x mit dem Wirkungsquerschnitt  $\sigma_x$  ist definiert als:

$$N_x = \sigma_x \cdot \mathcal{L} \tag{2.3}$$

Ziel der LHC-Experimente ist neben dem Nachweis des Higgs-Bosons die Suche nach neuen, im Standardmodell nicht enthaltenen Teilchen. Diese Teilchen haben Massen in der Größenordnung O(1 TeV), da bisherige Suchen den Bereich kleinerer Teilchenmassen bereits weitgehend ausschließen [2].

Für die Produktion dieser Teilchen werden sehr kleine Wirkungsquerschnitte erwartet. Zum einen fällt der Wirkungsquerschnitt bereits aus Dimensionsgründen proportional zu  $\frac{1}{m^2}$ . Weiterhin muss der Impulsbruchteil x der an der Produktion der Teilchen beteiligten Partonen in den Protonen vergleichsweise groß sein, damit Teilchen hoher Masse produziert werden können. Wegen des starken Abfalls der Strukturfunktion mit steigendem x [1], führt dies nochmal zu einer sehr starken Unterdrückung der Produktionswahrscheinlichkeit. Neue Teilchen können also nur dann entdeckt werden, wenn der Beschleuniger eine sehr hohe Luminosität hat.

Für den Large Hadron Collider, der in Kapitel 2.4 noch ausführlicher beschrieben ist, wird eine maximale Luminosität von  $L=10^{34}\,\mathrm{cm^{-2}s^{-1}}$  angestrebt. Dabei soll über die gesamte Laufzeit des LHC eine integrierte Luminosität von  $\mathcal{L}=300\,\mathrm{fb^{-1}}$  erreicht werden. Mit dem Luminositätsupgrade wird am zukünftigen HL-LHC dann eine fünffache Luminosität und eine zehnfache integrierte Luminosität angestrebt.

Eine hohe Luminosität ist nicht nur für die Entdeckung neuer Teilchen wichtig, sondern führt auch zur Erhöhung der Statistik und ermöglicht somit eine präzisere Vermessung schon bekannter Prozesse. Ein Beispiel hierfür ist die Vermessung des neu entdeckten Bosons, auf die aus aktuellem Anlass im Weiteren noch genauer eingegangen wird.

# 2.1 Das Standardmodell der Elementarteilchenphysik

Im Folgenden wird unter Verwendung der Bücher [1] und [3] das Standardmodell der Teilchenphysik beschrieben und aus diesem Grund auf die Angabe von Originalzitaten verzichtet, da diese in den Büchern zu finden sind.

Die uns bekannte stabile Materie lässt sich allein aus den Quarks und dem geladenen Lepton der ersten Familie, dem up- und down-Quark und dem Elektron aufbauen. Tatsächlich gibt es aber noch zwei weitere Familien von Teilchen mit größerer Masse. Diese werden in hochenergetischen Prozessen erzeugt, sie sind jedoch meist kurzlebig und zerfallen in die Teilchen der ersten Familie.

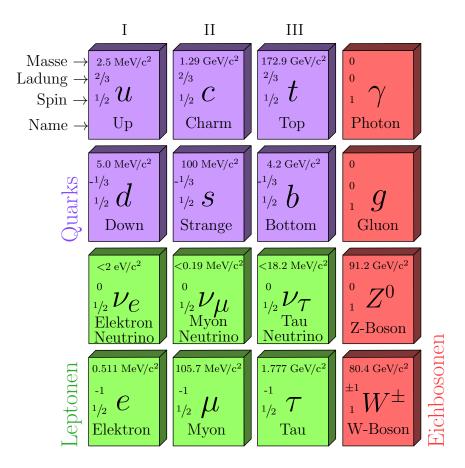

Eine Tabelle der elementaren Teilchen mit dessen Eigenschaften, wie Spin, Ladung und Masse ist in Abbildung 2.1 zu finden. Zu jedem Teilchen gibt es ein Antiteilchen, das die gleiche Masse und den gleichen Spin hat, allerdings umgekehrte Ladung und Parität. Neben den Fermionen mit Spin 1/2 sind in Abbildung 2.1 auch die Boso-

nen, die Spin 1 Austauschteilchen der elektromagnetischen, schwachen und starken Wechselwirkung, angegeben.

Abbildung 2.1: Die elementaren Teilchen des Standardmodells mit ihren Eigenschaften aufgeteilt in die 3 Fermionen-Familien (Quarks und Leptonen) und die Eichbosonen

Die Gravitation ist die bekannteste, aber zugleich schwächste Kraft, die erst zwischen sehr massiven Objekten spürbar wird. Das postulierte Austauschteilchen der Gravitation, das Graviton, ist noch nicht entdeckt worden und in Abbildung 2.1 nicht enthalten. Für die Experimente am LHC ist die Gravitation nicht relevant und wird deshalb hier nicht behandelt. Die elektromagnetische Kraft wirkt auf die elektrische Ladung — gleich geladene Objekte stoßen sich ab, entgegengesetzte Ladungen ziehen sich an. Die schwache Kraft ist für den  $\beta$ -Zerfall schwerer elementarer Teilchen verantwortlich, wie z.B. den Zerfall des Neutrons. Die starke Kraft bindet die Quarks im Hadron und gewährleistet, dass die Protonen im Atomkern sich aufgrund ihrer gleichen elektrischen Ladung nicht abstoßen. Stabile Kerne existieren, da die starke Kraft stärker als die elektromagnetische Kraft ist.

Im Standardmodell werden die drei Kräfte (starke, schwache und elektromagnetische Kraft) als Wechselwirkungen identifiziert, auf die im Folgenden genauer eingegangen wird.

### Die elektromagnetische Wechselwirkung

Die elektromagnetische Wechselwirkung wird durch die Eichtheorie der Quantenelektrodynamik (QED) beschrieben. Alle elektrisch geladenen Teilchen können elektromagnetisch wechselwirken. Das Austauschteilchen ist das Photon  $\gamma$ , das an die elektrische Ladung koppelt. Photonen sind masselos und tragen selbst keine Ladung.

#### Die schwache Wechselwirkung

Die schwache Wechselwirkung wirkt auf alle Fermionen. Die Austauschteilchen der schwachen Wechselwirkung sind das  $W^{\pm}$ - und Z-Boson. Im Gegensatz zu den Austauschbosonen der anderen Wechselwirkungen sind W- und Z-Boson massebehaftet [3]:

$$M_W = 80,403 \pm 0,029 \frac{\text{GeV}}{\text{cm}^2}$$

$M_Z = 91,188 \pm 0,002 \frac{\text{GeV}}{\text{cm}^2}$  (2.4)

Aufgrund ihrer Masse ist die Lebensdauer der Eichbosonen gering und ihre Reichweite kurz. Deshalb erscheint diese Wechselwirkung schwach.

Der bekannteste Prozess der schwachen Wechselwirkung ist der Beta-Zerfall, bei dem ein Elektron aus dem Atomkern emittiert wird, bzw. ein Neutron in ein Proton und ein Elektron unter Emission eines Elektron-Antineutrinos zerfällt:  $n \to e^- + \overline{\nu_e} + p$ . Die elektrisch- und farbneutralen Neutrinos sind die einzigen Teilchen, die ausschließlich schwach wechselwirken.

#### Die starke Wechselwirkung

Die Theorie der starken Wechselwirkung, die Quantenchromodynamik (QCD), basiert auf der Symmetriegruppe SU(3). Die starke Wechselwirkung koppelt an die Farbladung. Die drei Farben werden mit rot, grün und blau bezeichnet. Da Quarks eine Farbladung tragen, wirkt die starke Kraft auf Quarks bzw. Antiquarks.

Aus Quarks aufgebaute Teilchen werden Hadronen genannt. Da Hadronen farbneutral sind, gibt es zwei Arten: die Mesonen  $(q\overline{q})$  und die Baryonen (qqq). Baryonen bestehen aus drei Quarks, die jeweils eine unterschiedliche Farbladung tragen. Mesonen bestehen aus einem Quark-Antiquark-Paar, wobei das Antiquark die Antifarbe des Quarks trägt.

Die Austauschteilchen der QCD sind die Gluonen g, die an die Farbladungen koppeln. Jedes Gluon trägt eine Farbe und eine Antifarbe. Es ergeben sich insgesamt 8 Vektorgluonen, die die Farbkraft zwischen den Quarks übertragen können. Aufgrund der Farbladung können Gluonen auch an sich selbst koppeln.

### Die elektroschwache Vereinheitlichung

Die elektromagnetische und die schwache Wechselwirkung können durch eine einzige Theorie, die elektroschwache Wechselwirkung, beschrieben werden. Diese wurde von Glashow, Salam und Weinberg entwickelt und nennt sich auch GSW-Theorie.

Eine experimentelle Bestätigung der GSW-Theorie ergab sich durch den Nachweis des neutralen Stroms, der Entdeckung der W- und Z-Bosonen mit der erwarteten Masse und insbesondere den Präzisionsmessungen zur elektroschwachen Theorie bei LEP [4].

Die GSW-Theorie verwendet den Prozess der spontanen Symmetriebrechnung, welcher die Eichbosonen mit einer Masse versieht. Das wird durch das Einführen eines Isospindubletts erreicht. Der Higgs-Mechanismus sagt ein skalares, neutrales Teilchen, das Higgs-Boson, voraus.

Die fundamentalen Vektorbosonen sind das masselose Isospin-Triplett  $W^1_{\mu}$ ,  $W^2_{\mu}$  und  $W^3_{\mu}$  (aus der SU(2)-Gruppe) und das masselose Isospin-Singulett  $B_{\mu}$  (aus der U(1)-Gruppe). Infolge der spontanen Symmetriebrechung erhalten 3 Bosonen ( $W^+_{\mu}$ ,  $W^-_{\mu}$  und  $Z^0$ ) eine Masse und ein Boson ( $A_{\mu}$  entspricht dem  $\gamma$ ) bleibt masselos. Diese vier Bosonen sind eine Linearkombinationen aus  $W_{\mu}$  und  $B_{\mu}$  [1]:

$$W_{\mu}^{\pm} = \frac{1}{\sqrt{2}} \left( W_{\mu}^{(1)} \pm i W_{\mu}^{(2)} \right) \tag{2.5}$$

$$Z_{\mu} = W_{\mu}^{(3)} \cos \theta_W - B_{\mu} \sin \theta_W \tag{2.6}$$

$$A_{\mu} = W_{\mu}^{(3)} \sin \theta_W + B_{\mu} \cos \theta_W \tag{2.7}$$

Der Mischungswinkel  $\theta_W$  wird Weinberg-Winkel genannt. Er kann nicht theoretisch berechnet, sondern muss experimentell bestimmt werden.

# 2.2 Das Higgs-Boson

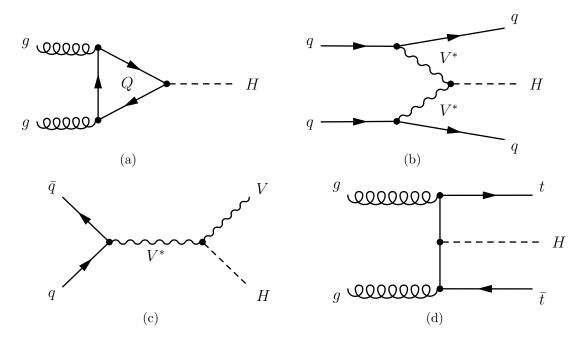

Das Higgs-Boson, genauer beschrieben in [5], koppelt an die Masse der Fermionen und Bosonen und somit bevorzugt an die schweren Teilchen des Standardmodells, wie W- und Z-Boson sowie Top- und Bottom-Quark. In Abbildung 2.2 sind die Feynmangraphen der vier hauptsächlichen Produktionsmechanismen des Higgs-Bosons in Proton-Proton Wechselwirkungen dargestellt. Diese bestehen aus der Fusion zweier

Gluonen  $gg \to H$ , der Vektor-Boson-Fusion  $qq \to V^*V^* \to qq + H$ , der assoziierten Produktion mit Vektorbosonen  $q\bar{q} \to V + H$  und der assoziierten Produktion mit einem  $t\bar{t}$ -Paar  $gg \to t\bar{t} + H$ .

Abbildung 2.2: Vier Produktionskanäle des Higgs-Bosons veranschaulicht in Feynmangraphen. Zu sehen sind (a) die Gluon-Gluon-Fusion, (b) die Vektor-Boson-Fusion, (c) die assoziierte Produktion mit einem Vektorboson und (d) die assoziierte Produktion mit einem  $t\bar{t}$ -Paar.

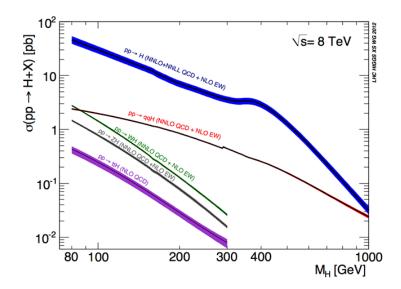

Abbildung 2.3: Produktionswirkungsquerschnitte für das Higgs-Boson bei einer Schwerpunktsenergie von  $\sqrt{s}$ =8 TeV als Funktion der Higgs-Masse [6]

In Abbildung 2.3 sind die Produktionswirkungsquerschnitte für das Higgs-Boson bei einer Schwerpunktsenergie von  $\sqrt{s}$ =8 TeV, der momentanen Schwerpunktsenergie des LHC, gezeigt. Zu sehen ist, dass die Gluon-Gluon-Fusion (pp  $\rightarrow$  H) den höchsten Wirkungsquerschnitt besitzt, während die Kanäle der Vektor-Boson-Fusion (pp  $\rightarrow$  qqH) etwa eine Größenordnung darunter liegen. Trotzdem ist die Vektor-Boson-Fusion für den LHC ein bedeutender Prozess, da zwei charakteristische Vorwärts-Jets erzeugt werden und keine (bzw. wenig) Kalorimeteraktivität im zentralen Bereich des Detektors erwartet wird.

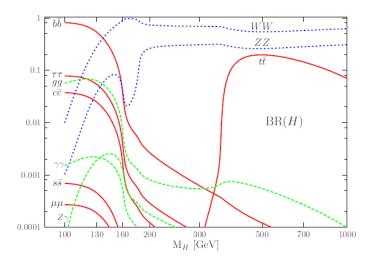

Die Abbildung 2.4 zeigt den gesamten erwarteten Higgs-Massenbereich. Da das Higgs bevorzugt an schwere Teilchen koppelt, zerfällt es auch vornehmlich in diese. Für hohe Massen zerfällt das Higgs fast ausschließlich in die Eichbosonen, mit einer Verteilung von  $2/3~H~\to~WW$  und  $1/3~H~\to~ZZ$ . Unterhalb der Schwelle zur Produktion eines WW-Paares ( $M_H \leq 135~{\rm GeV}$ ) dominieren die Zerfälle in ein reelles und ein virtuelles Vektorboson:  $H~\to~WW^*$  bzw.  $H~\to~ZZ^*$ . Für den leptonischen Zerfall beider Z-Bosonen im Fall  $H~\to~ZZ^*$  ist dieser Kanal aufgrund der 4 Leptonen im Endzustand gut vom Untergrund separierbar.

Abbildung 2.4: Die Verzweigungsverhältnisse für die Zerfallskanäle des Standardmodell-Higgs-Bosons für den gesamten erwarteten Massebereich. [5]

Im unteren Massenbereich des Higgs-Bosons bis etwa 135 GeV ist mit einem Verzweigungsverhältnis von 75 % bis 50 % der Zerfall in ein b-Quark-Antiquark-Paar  $H \to b\bar{b}$  dominant (siehe dazu Abbildung 2.4). Um diesen Kanal vom hohen QCD-Untergrund des LHC selektieren zu können, werden exzellente Vertexdetektoren benötigt, die die b-Quark-Jets mit hoher Effizienz und Reinheit von "leichten" Jets (u, d, c) identifizieren können.

Trotz seines geringen Verzweigungsverhältnisses ist der Zerfallskanal  $H \to \gamma \gamma$  sehr wichtig, da er aufgrund der besonders einfachen Signatur leicht zu identifizieren ist.

### Die Entdeckung eines neuen Bosons am LHC

Im Juli 2012 wurde die Entdeckung eines neuen Bosons bekannt gegeben. Die Experimente ATLAS und CMS haben mit  $5.9 \sigma$  bzw.  $5.8 \sigma$  Signifikanz ein neues Teilchen entdeckt [7,8]:

$$m_H = 126.0 \pm 0.4 \,(\text{stat}) \pm 0.4 \,(\text{sys}) \,\text{GeV}$$

(ATLAS) (2.8)

$$m_H = 125.3 \pm 0.4 \,(\text{stat}) \pm 0.5 \,(\text{sys}) \,\text{GeV}$$

(CMS)

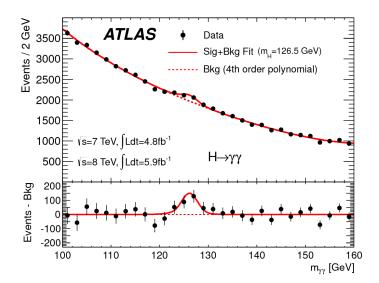

Für das ATLAS-Experiment sind die grundlegenden Daten für die Beobachtung des Bosons die kombinierten Daten aus 2011 mit einer inversen Luminosität von  $\mathcal{L} = 4.8 \, \mathrm{fb^{-1}}$  aufgezeichnet bei einer Schwerpunktsenergie von  $\sqrt{s} = 7 \, \mathrm{TeV}$  und den Daten aus 2012 mit  $\sqrt{s} = 8 \, \mathrm{TeV}$  bei  $\mathcal{L} = 5.8 \, \mathrm{fb^{-1}}$  [7].

Abbildung 2.5: Invariante Massenverteilung der 2 Photon-Kandidaten für die kombinierten Daten mit  $\sqrt{s} = 7 \text{ TeV}$  und  $\sqrt{s} = 8 \text{ TeV}$ . Das eingezeichnete Higgs-Signal entspricht einer Higgs-Masse von 126,5 GeV. Im unteren Bereich ist das verbleibende Signal nach Abzug der erwarteten Untergründe zu sehen. [7]

Abbildung 2.5 zeigt das invariante Massenspektrum für Ereignisse mit 2 Photonen. Im Massenbereich um  $m_{\gamma\gamma}=126\,\mathrm{GeV}$  sieht man ein deutliches Signal über dem erwarteten glatten Untergrund. Eine eindeutige Entdeckung des Boson konnte durch die Kombination von drei verschiedenen Zerfallskanälen des Higgs-Bosons  $H\to\gamma\gamma$ ,  $H\to WW\to l\nu l\nu$  und  $H\to ZZ\to llll$  erreicht werden.

Bei dem neuen Boson handelt es sich sehr wahrscheinlich um das Higgs-Boson. Eine direkte Bestätigung ist aber noch nicht möglich, da erst einige Eigenschaften des Higgs-Bosons bei dem entdeckten neuen Boson nachgewiesen werden konnten. Interessant ist es nun mit einer höheren Statistik weitere Zerfallskanäle des Higgs-Bosons zu erschließen und den Spin zu messen. Der Spin 1 ist bereits ausgeschlossen, da es einen Zerfall in zwei Photonen gibt. Es muss also geprüft werden, ob das Teilchen Spin 0 oder Spin 2 hat.

# 2.3 Physikalische Messungen am HL-LHC

Die Entdeckung und Vermessung seltener physikalischer Prozesse am LHC ist durch die bisher erreichte Luminosität begrenzt. Eine erhöhte Luminosität ist nötig, um seltene Prozesse eindeutig beobachten zu können. Der HL-LHC bietet ein breites Entdeckungspotential für Physik jenseits des Standardmodells und erlaubt es Ausschlussgrenzen im TeV-Bereich für Supersymmetrische Teilchen und andere Teilchen neuer Physik zu setzen, sowie Präzisionsmessungen des Higgs-Bosons durchzuführen. Als ein Beispiel für das Potential des HL-LHC wird im Folgenden auf die Möglichkeiten der Messungen in der Higgs-Physik eingegangen [9].

## Die Messung des Higgs-Bosons am HL-LHC

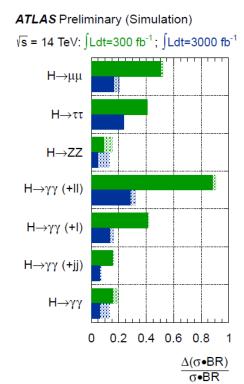

Die erhöhte Luminosität ergibt eine viel bessere Statistik für bereits entdeckte Kanäle und erlaubt seltene Higgs-Boson Produktions- bzw. Zerfallskanäle genauer zu untersuchen. Es werden neben den schon zur Entdeckung des Higgs-Bosons verwendeten Zerfallskanälen  $H \to \gamma \gamma$ ,  $H \to ZZ^*$  und  $H \to WW^*$  die Zerfälle des Higgs in ein Leptonpaar  $H \to \tau^+\tau^-$  sowie  $H \to \mu\mu$  und die assoziierte  $t\bar{t}$ -Higgs-Produktion mit dem Zerfall des Higgs in zwei Photonen  $t\bar{t} \to H \to t\bar{t}\gamma\gamma$  genauer gemessen werden können [9].

In Abbildung 2.6 ist die erwartete Präzision der Messung der Signalstärken in den verschiedenen Zerfallskanälen für die integrierten Luminositäten des LHC von  $\mathcal{L}=300\,\mathrm{fb^{-1}}$  und des HL-LHC von  $\mathcal{L}=3000\,\mathrm{fb^{-1}}$  zu sehen. Die Zerfälle des Higgs in die Endzustände  $\gamma\gamma$  und  $ZZ^*$  profitieren von der erhöhten Luminosität am stärksten. Der Zerfall  $H\to b\bar{b}$  ist in der Grafik nicht enthalten, da Jet-Energieauflösung und B-Hadron Identifikationseffizienz in Jets für die hohen Luminositäten noch nicht ausreichend analysiert sind.

Abbildung 2.6: Erwartete Präzision der Messungen der Signalstärken für die Design Luminositäten des LHC und des HL-LHC [9]

#### Die Messung der Higgs-Selbstkopplung am HL-LHC

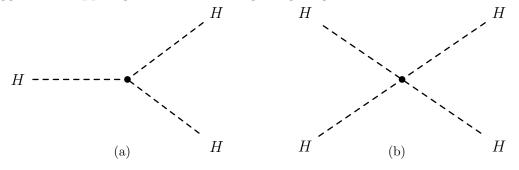

Der Test des Standardmodell-Higgs-Mechanismus ist die Messung der Higgs-Selbstkopplung am HL-LHC. Die Feynmangraphen für die Dreifach und die Vierfach-Higgs-Selbstkopplung sind in Abbildung 2.7 gezeigt.

Abbildung 2.7: Die Higgs-Selbstkopplung im Standardmodell. (a) Die Dreifach-Higgs-Selbstkopplung und (b) die Vierfach-Higgs-Selbstkopplung.

Eine direkte Beobachtung der Dreifach-Higgs-Kopplung über die Detektion von Higgs-Paarproduktionen ist für die Experimente am HL-LHC möglich. Als geeignete Kandidaten für die Entdeckung der Higgs-Selbstkopplung werden die Zerfälle

der Kanäle  $HH \to b\bar{b}W^+W^-$  und  $HH \to b\bar{b}\gamma\gamma$  angesehen. Die Erwartung ist, mit beiden Experimenten (ATLAS und CMS) zusammen mit dem Kanal  $HH \to b\bar{b}\gamma\gamma$  pro Experiment etwa 3  $\sigma$  Signifikanz zu erreichen [9].

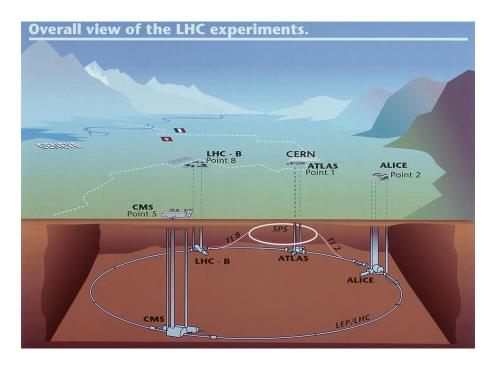

# 2.4 Das Upgrade des LHC zum HL-LHC

Am europäischen Kernforschungszentrum in Genf befindet sich der weltweit größte Proton-Protonbeschleuniger, der Large Hadron Collider. An seinen vier Wechselwirkungspunkten befinden sich die Experimente ATLAS, CMS<sup>1)</sup>, LHC-b<sup>2)</sup> und ALICE<sup>3)</sup>. Am LHC sollen in 40 MHz Protonkollisionen Schwerpunktsenergien von bis zu  $\sqrt{s} = 14 \,\text{TeV}$  erreicht werden. Es wird zudem eine maximale Luminosität von  $L = 10^{34} \,\text{cm}^{-2} \text{s}^{-1}$  angestrebt. Über die gesamte LHC-Betriebslaufzeit soll eine integrierte Luminosität von  $\mathcal{L} = 300 \,\text{fb}^{-1}$  erreicht werden [10].

Abbildung 2.8: Der Large Hadron Collider hat einen Umfang von 27 km und befindet sich in der Nähe von Genf in etwa 100 m unter der Erde. [11]

Knapp drei Jahre nach dem Start des LHC im Jahre 2009 wurde mit den kombinierten Daten bei Schwerpunktsenergien von  $\sqrt{s} = 7 \,\mathrm{TeV}$  und  $\sqrt{s} = 8 \,\mathrm{TeV}$  die erste wichtige Entdeckung eines neuen Bosons gemacht.

<sup>1)</sup> Compact Muon Solenoid

<sup>&</sup>lt;sup>2)</sup>Large Hadron Collider beauty

<sup>&</sup>lt;sup>3)</sup>**A** Large Ion Collider Experiment

Das Upgrade des LHC zum HL-LHC unterteilt sich in drei Phasen, die im Folgenden kurz aufgeführt sind [12]:

- Phase 0 Upgrade: Nach der ersten längeren Umbauphase im Jahr 2013/2014 soll der LHC die vorgesehene Schwerpunktsenergie von  $\sqrt{s} = 14$  TeV erreichen, sowie die Design-Luminosität von L =  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> liefern.

- Phase 1 Upgrade: Nach einer angesammelten integrierten Luminosität von etwa  $\mathcal{L} = 100\,\mathrm{fb^{-1}}$  wird eine weitere Umbauphase des LHC die Verdopplung der Luminosität auf etwa L =  $2, 2 \cdot 10^{34}\,\mathrm{cm^{-2}s^{-1}}$  zur Folge haben. Bis 2021 sollen  $\mathcal{L} = 300\text{-}400\,\mathrm{fb^{-1}}$  mit dem LHC erreicht werden.

- Phase 2 Upgrade: In einer dritten Phase, geplant für das Jahr 2022, wird der Umbau zum HL-LHC durchgeführt, mit dem bei gleichen Energien eine Luminosität von L =  $5 \cdot 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> angestrebt wird. Es soll eine integrierte Luminosität von  $\mathcal{L} = 3000$  fb<sup>-1</sup> erreicht werden, davon  $\mathcal{L} = 2500$  fb<sup>-1</sup> am HL-LHC.

Die Prototypen dieser Arbeit wurden alle für das Phase 2 Upgrade des ATLAS-Detektors entwickelt.

## 2.5 Der ATLAS-Detektor für den HL-LHC

Um den Aufbau des zukünftigen ATLAS-Detektors für das Upgrade zum HL-LHC im Jahr 2022 besser erklären zu können, wird zunächst kurz auf den momentanen ATLAS-Detektor eingegangen.

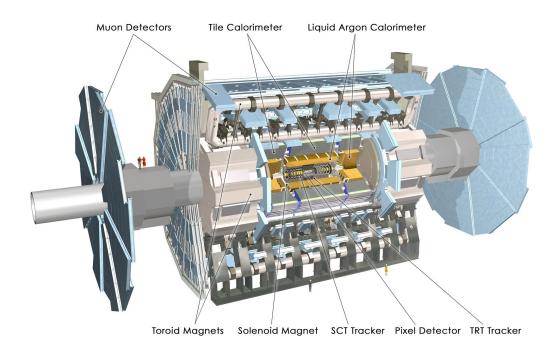

#### Der ATLAS-Detektor

Der in Abbildung 2.9 gezeigte ATLAS-Detektor ist ein zylindrisch aufgebauter, um den Wechselwirkungspunkt symmetrischer Vielzweckdetektor. Er besteht aus einem inneren Spurdetektor umgeben von einem dünnen, supraleitenden Solenoid, der ein 2 Tesla Magnetfeld erzeugt, dem elektromagnetischen und dem hadronischen Kalorimeter und einem Myon-Spektrometer.

Der innere Spurdetektor dient einer sehr genauen Vertexrekonstruktion sowie der präzisen Impulsmessung geladener Teilchen. Der Pixeldetektor erreicht mit seinen ca. 80 Millionen Auslesekanälen die höchste Auflösung im gesamten ATLAS-Detektor. Die Silizium-Detektoren, der Pixel- und der Streifen-Detektor<sup>4)</sup> haben eine Ab-

<sup>&</sup>lt;sup>4)</sup>SCT, **S**emi**c**onductor **T**racking

Abbildung 2.9: Der ATLAS-Detektor ist 44 m lang, hat einen Durchmesser von 22 m und ist 7000 t schwer. Es können mit dem ATLAS-Detektor Datenraten bis zu 40 MHz verarbeitet werden. [11]

deckung von  $\eta \leq 2,5^5$ . Auf den SCT folgt der Übergangsstrahlungsdetektor TRT<sup>6</sup>. Dieser Detektor besteht aus Drahtkammer-Röhrchen mit einem Durchmesser von 4 mm, die mit Gas gefüllte Driftkammern sind. Diese liefern eine hohe Zahl an Spurpunkten, aber eine geringe Auflösung in z-Richtung. Im TRT werden geladene Teilchen nachgewiesen. Durch die Erzeugung von Übergangsstrahlung durch relativistische Teilchen im TRT können Elektronen von anderen geladenen Teilchen unterschieden werden.

Das elektromagnetische Kalorimeter besteht aus sich abwechselnden Schichten von Flüssig-Argon und einer akkordeonartig aufgebauten Bleiabsorberstruktur mit Kapton-Elektroden. Es ist aufgeteilt in Barrel- und Endkappenbereich. Die Raumwinkelabdeckung beträgt  $\eta \leq 1,5$  im Zentralbereich und  $\eta \leq 3,2$  im Vorwärtsbereich.

Das hadronische Kalorimeter ist unterteilt in Tile-Kalorimeter, Endkappenkalorimeter und Vorwärtskalorimeter. Das Tile-Kalorimeter besteht abwechselnd aus Stahlplatten für den Absorber und Szintillatorkacheln als aktives Material.

<sup>&</sup>lt;sup>5)</sup>Die Pseudorapidität  $\eta$  ist eine räumliche Koordinate, die anstelle des Polarwinkels  $\theta$  verwendet wird, um den Winkel eines Vektors relativ zur Strahlachse anzugeben. Die Pseudorapidität wird definiert durch  $\eta = -\ln(\tan\frac{\theta}{2})$ .

<sup>&</sup>lt;sup>6)</sup>Transition Radiation Tracker

Das Endkappen- und das Vorwärtskalorimeter sind zusammengesetzt aus Kupferplatten und Flüssigargonbereichen, die den aktiven Bereich zum Messen der Hadronen darstellen. Das gesamte hadronische Kalorimeter dient der Rekonstruktion von Jets und der Messung fehlender transversaler Energie in physikalischen Prozessen und deckt einen Bereich von maximal  $\eta \leq 4.9$  ab.

Das Myonspektrometer befindet sich im äußersten Bereich des ATLAS-Detektors, den nur noch Myonen und nur indirekt nachweisbare Neutrinos durchdringen können. Es besteht aus präzisen Spurkammern, welche zur Spurrekonstruktion der im Magnetfeld abgelenkten Myonen dienen, und aus einem separaten Trigger-Bereich, der schnelle Trigger-Informationen (< 25 ns) liefert. Die verschiedenen Myonkammern nutzen alle die Gasverstärkung in Proportionalkammern oder Röhren. Drei große supraleitende Toroide erzeugen ein Magnetfeld von etwa 4 Tesla senkrecht zur Flugrichtung der Myonen. Während die Myonkammern den Bereich von  $\eta \leq 2,7$  abdecken, sind die Trigger auf einen Bereich von  $\eta \leq 2,4$  beschränkt.

Das Triggersystem des ATLAS-Detektors ist dreistufig und besteht zunächst aus dem Level 1 Trigger. Dieser nutzt Teile des elektromagnetischen und hadronischen Kalorimeters, sowie den Myontrigger, um physikalisch interessante Signaturen zu detektieren. Der Level 1 Trigger erlaubt eine Reduktion der Datenrate von 40 MHz auf 75 kHz. Der darauf folgende High-Level-Trigger besteht aus Level 2 Trigger und Event-Filter, auf denen eine entsprechende Software das Ereignis genauer analysiert und so die Datenmenge auf 200 Hz reduziert.

### Der zukünftige ATLAS-Detektor

Durch das Upgrade des LHC zum HL-LHC wird der ATLAS-Detektor in einer etwa zehnfach höheren Strahlungsumgebung<sup>7)</sup> und Spurdichte im Vergleich zum gegenwärtigen Betrieb voll funktionsfähig sein müssen. Von den erforderlichen Umbaumaßnahmen ist vor allem der Spurdetektor betroffen, der im Phase 2 Upgrade komplett erneuert werden wird. Die Hauptgründe hierfür sind die schon bestehenden Strahlenschäden am Detektor und die höheren Belegungsdichten durch höhere Teilchenraten. Diese Teilchenraten führen auch zu einer Vergrößerung der Datenauslesegeschwindigkeit.

Der TRT wird die erhöhten Teilchen- und schnelleren Datenraten nicht mehr verarbeiten können, so dass dieser komplett durch einen Silizium-Detektor ersetzt werden wird.

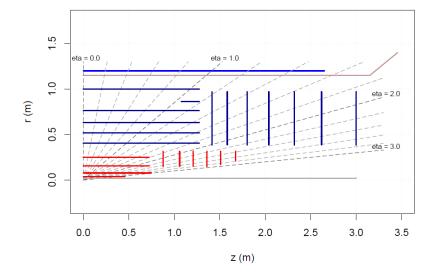

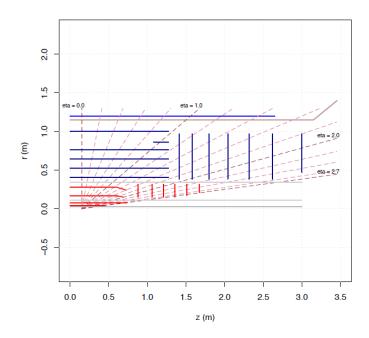

Der zukünftige Spurdetektor wird deshalb folgendermaßen für das Phase 2 Upgrade geplant: Im inneren Bereich werden sich Pixelsensoren befinden, die von Mikrostreifen-Sensoren umgeben sind. In Abbildung 2.10 ist das Layout des geplanten Spurdetektors zu sehen. In rot sind die 4 Lagen des Pixeldetektors im Zentralbereich und die 6 Pixel-Endkappen im entsprechenden Abstand zur Strahlachse eingezeichnet.

<sup>&</sup>lt;sup>7)</sup>Die genaue Strahlungsumgebung für HL-LHC wird in Kapitel 4.2.1 diskutiert.

Abbildung 2.10: Das Baseline-Layout des geplanten Spurdetektors. [12] Gezeigt sind die Lagen des Barrel- und des Endkappenbereichs des Pixeldetektors (rot) und des Streifendetektors (blau) in Abhängigkeit des Abstandes zum Wechselwirkungspunkt in z-Richtung und zum radialen Abstand der Strahlachse r.

Auf den genauen Aufbau des Pixeldetektors wird in Kapitel 2.6 noch ausführlicher eingegangen. In blau sind die Lagen des Streifendetektors eingezeichnet: Es folgen 3 Streifen-Lagen (mit kurzen Streifen-Modulen) und 2 Streifen-Lagen (mit langen Streifen-Modulen) auf den Pixeldetektor im Zentralbereich. Im Vorwärtsbereich sind 7 Streifen-Endkappen geplant. Zwischen den letzten Streifen-Lagen ist in der Abbildung 2.10 noch eine kurze eingeschobene Lage eingezeichnet, der "Stub-barrel". Dieser wird eingeführt, um ein Loch in der Treffer-Abdeckung zwischen Zentral- und Endkappenbereich des Streifendetektors zu verhindern. Die Raumwinkelabdeckung des Spurdetektors mit insgesamt etwa 700 Millionen Auslesekanälen soll  $|\eta| < 2,5$  betragen. Um den Spurdetektor ist in Abbildung 2.10 noch eine weitere Lage in hellerem blau eingezeichnet, die aus einem Polyethylen-Moderator besteht und die den Neutronenfluss ausgehend von den Kalorimetern reduzieren soll.

Die erhöhte Teilchenrate benötigt eine Erneuerung der Ausleseelektronik der Kalorimeter. Die Front-End-Elektronik wird aufgrund der schon erfolgten Strahlenschädigung durch den LHC-Betrieb zu stark durch Strahleneffekte geschädigt sein und muss ausgetauscht werden. Somit kann sie auch gleichzeitig für die höheren Datenraten verbessert werden. Auch die Triggerelektronik wird verbessert. Es wird ein zusätzlicher Level 0 Trigger eingebaut, der die Daten auf eine Rate von 500 kHz reduzieren wird, bei einer maximalen Latenzzeit von 6  $\mu$ s. Dieser Trigger wird auch Informationen vom Spurdetektor mit in die Auswahl der geeigneten Daten einfließen lassen.

Für die Myonkammern und die Myontrigger ergeben sich die gleichen Einschränkungen wie für die anderen Detektoren.

Unter der Berücksichtigung einer erhöhten Strahlenumgebung und einer viel höheren Teilchenrate muss der Detektor genauso performant sein wie der momentane ATLAS-Detektor.

## 2.6 Der ATLAS-Pixeldetektor für den HL-LHC

Das bisher geplante Layout des zukünftigen Pixeldetektors basiert auf den Erfahrungen mit dem momentanen Spurdetektor vereint mit den Anforderungen für den HL-LHC. Aufgrund der viel höheren Teilchenraten im Betrieb des HL-LHC muss die Geschwindigkeit der Datenauslese im Pixeldetektor erhöht sowie eine höhere Auflösung der Pixel erreicht werden, um die Belegungsdichte zu reduzieren. Es soll eine gute zwei Teilchen Separation ermöglicht werden, da die Hauptaufgabe des Pixeldetektors die Vertexrekonstruktion ist.

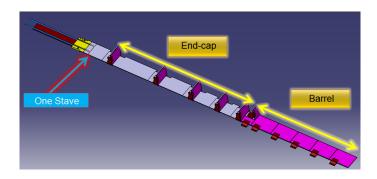

Grundlage für den geplanten Pixeldetektor sind die Pixelmodule, also die aktiven Sensoren, die mit der Ausleseelektronik verbunden sind. Die Sensoren sind mit den Auslesechips (Front-End-Chips) elektrisch kontaktiert. Die Module sind auf langen Trägerstrukturen, sogenannten Staves, aufgeklebt. Insgesamt soll es im Zentralbereich des Detektors 4 Lagen dieser Staves geben sowie 6 Endkappen. Darauf sollen sich Pixelmodule mit unterschiedlichen Zahlen an FE-Chips (2, 4 und 6) befinden.

Die innersten beiden Lagen des Pixeldetektors sollen separat auswechselbar aufgebaut sein und werden deshalb in der Inner Support Tube (= IST) zusammengefasst, welche einen Außenradius von 110 mm hat. Für die Module in der IST ist eine Pixelfläche von  $25 \times 150 \,\mu\text{m}^2$  geplant.

Wiederum separat montierbar sollen die anderen beiden Lagen im Zentralbereich des Detektors zusammen mit den Disks in der Pixel Support Tube (= PST) zusammengefasst werden. Für die PST ist ein Außenradius von 345 mm geplant. Die Pixelflächen der Module in der PST sind mit  $50 \times 250 \,\mu\text{m}^2$  größer als die der IST.

In Tabelle 2.1 sind die Zahlen der Pixelmodule in der Summe und pro Stave bzw. Disk Sektor zu finden. Für die Disks wurden die Zahlen für die 6-fach und die 4-fach-Module zusammengefasst. Nur die Module der innersten Lage sind Module mit 2 Sensoren.

Die Art der Sensoren ist für den geplanten Pixeldetektor noch offen. Es stehen 3 verschiedene Sensortypen zur Auswahl: Planare Sensoren, 3D-Sensoren und Diamant-Sensoren. Die planaren Sensoren sind schon vielfach eingesetzt worden und dementsprechend ist die Erfahrung mit ihnen sehr groß. Außerdem sind planare Sensoren im Vergleich die kostengünstigsten. Sie sind allerdings nicht so strahlenhart. 3D-Sensoren sind aufgrund ihrer kleineren Depletionsfläche toleranter gegenüber Strah-

| Lage/Disk | Zahl der Module      | Module pro Stave | Zahl der FE-Chips |

|-----------|----------------------|------------------|-------------------|

|           | (2,4 und 6 Sensoren) | /Disk Sektor     | pro Modul         |

| Lage 1    | 352                  | 22               | 2                 |

| Lage 2    | 576                  | 36               | 4                 |

| Lage 3    | 1120                 | 35               | 4                 |

| Lage 4    | 1785                 | 35               | 4                 |

| Disk 1    | 288                  | 12               | 6 bzw. 4          |

| Disk 2    | 288                  | 12               | 6 bzw. 4          |

| Disk 3    | 288                  | 12               | 6 bzw. 4          |

| Disk 4    | 288                  | 12               | 6 bzw. 4          |

| Disk 5    | 296                  | 13               | 6 bzw. 4          |

| Disk 6    | 216                  | 9                | 6 bzw. 4          |

Tabelle 2.1: Die Zahl der Module im zukünftigen Pixeldetektor

lenschäden. Sie benötigen nur eine geringe Depletionsspannung, sind aber in der Produktion teurer. Die Diamant-Sensoren haben den großen Vorteil, dass sie sehr strahlenhart sind und zusätzlich keine Kühlung brauchen. Von Nachteil ist, dass Diamant-Sensoren hohe Kosten verursachen — vor allem für einen Detektor mit einer solch großen Sensorzahl.

Der FE-Chip digitalisiert die Daten<sup>8)</sup> der Sensoren und gibt diese an die End-Of-Stave-Karte (= EoS-Karte) weiter. Für die inneren Lagen des Pixeldetektors wird aufgrund der kleineren Sensorgröße ein neues FE-Design benötigt. Die FE-Chips werden im 65 nm Prozess realisiert werden. Für die äußeren Lagen soll der sich auch in der Entwicklung befindende FEI4<sup>9)</sup> in modifizierter Form eingesetzt werden.

Die Datenrate beträgt voraussichtlich 2,5 GBits/s für die inneren und 640 MBit/s für die äußeren Lagen. Vom FE-Chip werden die Daten auf der EoS-Karte vom Giga-Bit Transceiver (= GBT)zusammengefasst und an den optischen Link weitergegeben, der die elektrischen Signale in optische umwandelt.

Die FE-Chips produzieren im Betrieb eine nicht vernachlässigbare Wärme. Aus diesem Grund muss der Detektor gekühlt werden. Angestrebt wird eine CO<sub>2</sub> Verdampfungskühlung, die über sehr dünne Röhrchen, die sich in den Staves befinden, die Wärme im Detektor abführt.

Das endgültige Layout des zukünftigen Pixeldetektors steht noch nicht fest. Momentan werden drei verschiedene Layouts diskutiert: Das Conical Layout, das Alpine Layout und das 5-Pixel-Lagen Layout.

<sup>&</sup>lt;sup>8)</sup>Mithilfe der Methode der "Time Over Threshold" wird die deponierte Ladungsmenge in den Pixel-Zellen bestimmt.

<sup>&</sup>lt;sup>9)</sup>Der FEI4 wird zur Zeit für das IBL-Upgrade im Jahr 2013 entwickelt, bei dem der Pixeldetektor eine zusätzliche innere Lage erhält.

Abbildung 2.11: Das Conical Layout als eine von drei Optionen für das zukünftige Pixel-Layout [12]

Beim Conical Layout sind die Enden des Staves in Richtung der Strahlachse gebogen, wie in Abbildung 2.11 zu sehen ist. Diese Bauweise erlaubt einen größeren Radius für die äußeren Pixellagen (zur besseren Spurrekonstruktion), ohne eine zu große Lücke zu den Endkappen zu erzeugen. Des Weiteren können die Endkappen näher am Zentralbereich angebracht werden, was vorteilhaft für die mechanische Stabilität des Detektors ist. Durch die konische Bauweise können die EoS-Karten auf höhere Pseudorapiditäten (vgl. Abbildung 2.11) gebracht werden, so dass das inaktive Material im Zentralbereich reduziert wird.

Abbildung 2.12: Veranschaulichung des Alpine Stave Layouts [13]

Bei der Option des Alpine Layout für den Pixeldetektor werden die Module des Endkappenbereichs auf eine keilförmige Trägerstruktur angebracht. Dadurch wird Material für den Bau der Endkappen eingespart. Eine Veranschaulichung dieses Layouts ist in Abbildung 2.12 gezeigt.

Als dritte Option wird die Erweiterung um eine Pixellage in Erwägung gezogen. Ob die Staves im Zentralbereich dabei alle dieselbe Länge haben werden oder ob die äußeren Lagen kürzere Staves im Zentralbereich haben werden, wird noch diskutiert.

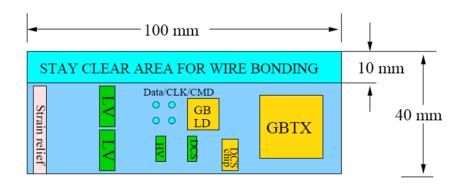

## 2.6.1 Die End-Of-Stave-Karte

Für das Phase 2 Upgrade des ATLAS-Detektors ist geplant, dass die Module eines halben Staves jeweils eine Gruppe ergeben. Jede Modul-Gruppe soll gemeinsame Leitungen für die Ein- und Ausgänge der Datenübertragung, der Versorgung mit Hochspannung und Niederspannung sowie Leitungen für das Detektor-Kontroll-System erhalten. Alle diesen elektrischen Leitungen sollen über die End-Of-Stave-Karte (= EoS-Karte) aus dem Detektor geführt werden. Es ist geplant, dass sich an jedem Ende der Staves eine EoS-Karte befinden wird. Das bedeutet, pro Stave soll es 2 EoS-Karten geben.

Zusätzlich zu den elektrischen Leitungen soll die EoS-Karte auch aktive Komponenten beinhalten. Zum Einen befindet sich dort der GBT, der die physikalischen Daten vom Detektor an den optischen Link weiter gibt und umgekehrt die Daten zu den jeweiligen Detektormodulen sendet. Es wird diskutiert, ob für den Pixeldetektor die optische Datenübertragung auf der EoS-Karte beginnen kann, da dort die Strahlungsumgebung noch zu hoch ist. Der optische Link, der für die Umwandlung der elektrischen Signale in optische zuständig ist, würde sich dann weiter außerhalb befinden. Neben dem GBT ist auch der DCS-Chip auf der EoS-Karte lokalisiert. Dieser wird Informationen über die Modultemperaturen und Spannungen erhalten und diese über den DCS-Controller zum Kontrollraum senden. Wie der DCS-Chip diese Daten erhält, steht noch nicht fest. Eine genaue Beschreibung der Funktionalität des DCS-Chips und des DCS-Controllers wird im folgenden Kapitel gegeben.

Abbildung 2.13: Schema der End Of Stave Karte [14]

Das Schema der voraussichtlichen EoS-Karte ist in Abbildung 2.13 zu sehen. In grün sind die Stecker für die Versorgungsleitungen eingezeichnet und in gelb die aktiven Komponenten, wie DCS-Chip, Giga-Bit Transceiver (GBTX) und Giga-Bit Laser Driver (GB LD). Die Größe der EoS-Karte wird voraussichtlich  $40 \times 100 \, \mathrm{mm^2}$  betragen. Das Layout der EoS-Karte für die innerste Pixellage wird aufgrund der größeren Zahl an Auslesekanälen etwas anders aussehen. Es wird sich auf diesen EoS-Karten die Zahl der Komponenten pro Karte erhöhen.

# Kapitel 3

# Das Kontrollsystem für den zukünftigen ATLAS-Pixeldetektor

Das Detektor-Kontrollsystem überwacht und steuert alle Parameter, die zum zuverlässigen Betrieb des Detektors notwendig sind. Es gewährleistet zudem ein komfortables Ein- bzw. Ausschalten des Detektors. Zusätzlich dazu reagiert das Kontrollsystem im Falle eines Fehlers und kann den Detektor kontrolliert vor Schädigung bewahren und somit eine optimale Datennahme garantieren. Diese Fehler können durch Überhitzung, einen zu hohen Stromverbrauch oder auch durch eine zu hohe Luftfeuchtigkeit verursacht werden. Tritt solch ein Fall auf, sind die Detektor-Komponenten unmittelbar gefährdet und müssen vom Kontrollsystem geschützt werden. Deshalb überwacht das Detektor-Kontrollsystem permanent Temperaturen, Spannungen und Ströme der Detektor-Komponenten.

Für die Analyse der physikalischen Daten liefert das Kontrollsystem die nötigen Informationen, um die Qualität der Daten zu bestimmen. Nur qualitativ hochwertige Daten, die wirklich physikalische Informationen enthalten, können für die Analysen verwendet werden. Dabei ist es wichtig, eine minimale integrierte Luminosität zu erreichen, und zusätzlich dürfen keine größeren Fehler im Trigger-System, bei der Datennahme oder im Detektor aufgetreten sein.

Das Detektor-Kontrollsystem ermöglicht also eine einfache Bedienung des Detektors und unterstützt den reibungsfreien Ablauf der Datennahme. Deshalb muss solch ein System sehr robust aufgebaut sein, damit es in jedem Fall einwandfrei reagieren kann und keine Fehler verursacht.

Die Schwierigkeit besteht darin, ein solches System unter der Voraussetzung aufzubauen, das Material des zukünftigen Detektors zu reduzieren, obwohl dieser eine mehr als dreifache Anzahl an Auslesekanälen haben wird. Betrachtet man dies unter dem Aspekt der um das zehnfach angestiegenen Strahlungsumgebung im Pixeldetektor, wird schnell klar, dass das Konzept des bisherigen Kontrollsystems nicht übernommen werden kann.

# 3.1 Anforderungen an das Detektorkontrollsystem

Wie oben schon beschrieben, garantiert das Detektor-Kontrollsystem eine reibungsfreie Datennahme sowie die Sicherheit des Detektors.

Für den DCS-Operator müssen benutzerfreundliche Software-Programme vorhanden sein, damit dieser den Detektor sicher steuern und überwachen kann. Eine direkte Rückmeldung nach der Änderung einer Betriebsgröße des Detektors, wie z.B. des Stroms oder der Spannung, ist dringend notwendig, um auf kritische Situationen umgehend reagieren zu können. Der Status der Detektorversorgung, der Kühlung sowie der Detektorumgebung muss permanent bekannt sein.

Des Weiteren muss das zukünftige ATLAS-Pixel-DCS die neuen Ansätze für die Inner TracKer (= ITK) Detektorversorgung berücksichtigen. Es sind zwei verschiedene Versorgungsansätze in der Diskussion: die serielle und die parallele Versorgung des Detektors.

Für die Komponenten innerhalb des Detektorvolumens muss zudem berücksichtigt werden, dass der Leistungsverbrauch so gering wie möglich zu halten ist, denn die vom Verbraucher verursachte Wärme muss während des Detektorbetriebs abgeführt werden, was nur begrenzt möglich ist. Außerdem soll das Kontrollsystem auch bei ausgeschaltetem Detektor<sup>1)</sup> funktionsfähig sein, also auch wenn keine Kühlung des Detektors vorhanden ist.

Eine weitere wichtige Anforderung an das zukünftige Detektor-Kontrollsystem ist die angestrebte Materialreduktion im Pixel-Detektorvolumen. Die Zahl der Detektor-Module verdreifacht sich knapp, wobei der zur Verfügung stehende Platz unverändert bleibt. Es muss also die Zahl der Versorgungsleitungen reduziert werden.

Aufgrund der zehnfach höheren Strahlungsumgebung des ATLAS-Detektors bei HL-LHC müssen die DCS-Komponenten im Detektor sehr strahlenhart sein. Für diese Komponenten muss die höchste Zuverlässigkeit garantiert werden, da der gesamte Pixeldetektor nach Inbetriebnahme nicht mehr erreichbar ist und keine Komponente repariert oder ausgetauscht werden kann.

Zusätzlich zu den bisherigen Anforderungen muss der Detektor vor Überhitzung geschützt werden, falls ein Fehler im Kühlsystem oder eine extreme lokale Erhitzung des Detektors auftritt.

Zuletzt ist es wichtig, dass die Integration des Pixel-DCS-Systems in das ATLAS-DCS-System gewährleistet ist, damit im späteren Betrieb mehrere ATLAS-Subdetektoren gleichzeitig überwacht und gesteuert werden können.

Die Überwachungsgrößen des zukünftigen DCS-Systems sind in Tabelle 3.1 dargestellt. Aufgrund der Anforderungen an das System variieren sie mit der Präzision, Verfügbarkeit, Granularität und Zuverlässigkeit.

$<sup>^{1)}\</sup>mathrm{Diese}$  Funktion des Kontrollsystems ist notwendig für Tests (z.B. Kabeltests), aber auch zur Kalibration des Detektors.

| Detektorbereich  | Parameter        | Kontrollgröße                        |  |

|------------------|------------------|--------------------------------------|--|

| -                |                  | Ein/Aus                              |  |

|                  | Niederspannung   | Überwachung von Strom und Spannung   |  |

|                  |                  | Steuerung der Betriebsparameter      |  |

|                  |                  | Ein/Aus                              |  |

| Detektormodul    | Hochspannung     | Überwachung von Strom und Spannung   |  |

|                  |                  | Einstellbarkeit der Betriebsspannung |  |

|                  | Temperatur       | Überwachung der Temperatur           |  |

|                  |                  | Schutz vor Überhitzung               |  |

|                  |                  | Ein/Aus                              |  |

|                  | Niederspannung   | Überwachung von Strom und Spannung   |  |

|                  |                  | Steuerung der Betriebsparameter      |  |

| EoS-Karte        | Temperatur       | Überwachung der Temperatur           |  |

|                  | Neu-             | Senden eines Reset-Signals           |  |

|                  | start            | Überwachung des Reset-Signals        |  |

| Detektorumgebung | Temperatur       | Überwachung der Temperatur           |  |

|                  | relative Feuchte | Überwachung der Feuchteumgebung      |  |

Tabelle 3.1: Die Überwachungsgrößen des zukünftigen Detektor-Kontrollsystems

Eine DCS-Ausleseeinheit wird voraussichtlich jeweils aus Gruppen von acht Detektor-Modulen bestehen, einer sogenannten Versorgungseinheit.

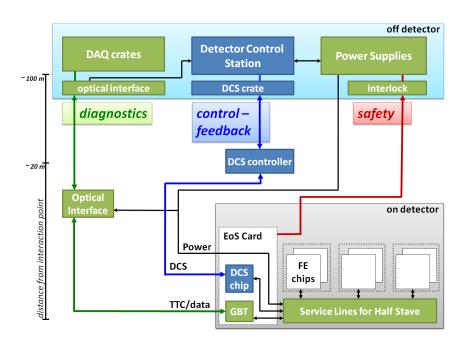

# 3.2 Aufbau des zukünftigen DCS

Aus den Anforderungen an das zukünftige Detektor-Kontrollsystem heraus wurde das im Folgenden beschriebene System entwickelt. Dieses ist in drei Pfade unterteilt, welche sich in Verfügbarkeit und Granularität unterscheiden, so dass der Detektor einerseits vollständig automatisch gegenüber Überhitzung abgesichert ist (Safety-Pfad), aber auch möglichst detaillierte Informationen über den Zustand des Detektors jederzeit (Control- und Feedback) und auf Abruf noch detaillierter (Diagnostics-Pfad) vorliegen.

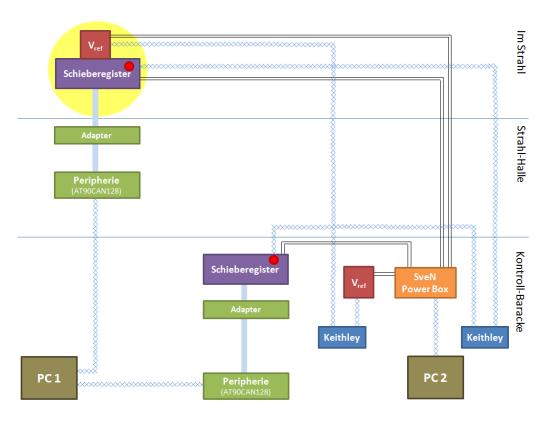

In Abbildung 3.1 ist die komplette Architektur des zukünftigen Kontrollsystems abgebildet. Im oberen Bereich ist die sich im Counting Room<sup>2)</sup> befindende Elektronik zu sehen, bestehend aus Datennahme-Ausleseelektronik (DAQ crates), Detektor-Kontroll-Stationen (mehrere Rechner, auf denen sich die Software für das DCS befindet) und den Versorgungseinheiten des Detektors. In ca. 100 m Entfernung be-

<sup>&</sup>lt;sup>2)</sup>Es gibt bei ATLAS zwei Counting Rooms. Dies sind Hallen, in denen sich die Ausleseelektronik befindet und wo keine hohe Strahlenbelastung herrscht.

Abbildung 3.1: Der Aufbau des zukünftigen Detektorkontrollsystems [15]

findet sich das Volumen des Pixeldetektors, von dem eine Ausleseeinheit bestehend aus Half-Stave und EoS-Karte zu sehen ist.

Die drei DCS-Pfade sind in Abbildung 3.1 farblich getrennt. In grün ist der Weg der DCS-Daten eingezeichnet, welche im Diagnostics-Pfad über den optischen Datenpfad mitgesendet werden. In blau sind die Komponenten des Control und Feedback Pfades eingezeichnet und in rot ist der Safety-Pfad dargestellt. Im Folgenden wird nun im Detail auf den Aufbau und die Funktion der einzelnen DCS-Pfade eingegangen.

## Der Safety-Pfad

Der Safety-Pfad, oder auch das Interlocksystem, wird als komplett eigenständiges, statisch verdrahtetes System aufgebaut. Die Ausleseelektronik ist im Kontrollraum lokalisiert, von dem aus die Leitungen zu den Temperatursensoren im Detektor geführt werden. Im Pixeldetektor werden sich jeweils ein Temperatursensor pro Versorgungseinheit und zwei Sensoren pro Kühlkreis auf der Kühlstruktur befinden. Des Weiteren könnten zusätzliche Temperatursensoren an verschiedenen kritischen Stellen, an denen die Wärme nicht sehr gut abtransportiert werden kann, eingebaut werden. Im Falle einer Überhitzung werden Teile des Detektors über das Interlocksystem direkt an den Versorgungseinheiten, die sich auch im Kontrollraum befinden, abgeschaltet. Im Normalfall sollte bei einem ungewöhnlichen Temperaturanstieg der Detektor-Komponenten schonender für die Elektronik vorgegangen und eine gewisse Abschaltreihenfolge durch ein automatisiertes DCS-Skript eingehalten werden. Ist das aber nicht der Fall, so muss das Interlocksystem eingreifen.

Das Interlocksystem muss stets betriebsbereit sein, also für jeden Zustand des Detektors (während der Installation, Kabeltests, Kalibration, Datennahme etc.) funktionieren. Außerdem muss das Interlocksystem absolut fehlerfrei reagieren können, um einerseits die Detektor-Komponenten nicht zu gefährden, aber andererseits auch nicht fälschlicherweise Teile des Detektors auszuschalten. Deshalb wird es, genauso wie das momentane Interlocksystem, komplett eigenständig und zudem unabhängig von Softwareroutinen aufgebaut werden. Das bedeutet allerdings, dass die Granularität dieses Systems sehr stark eingeschränkt werden muss, um den Leitungsverbrauch so gering wie möglich zu halten. Es ist aber auch nicht unbedingt notwendig, einzelne Detektormodule bei einem starken Temperaturanstieg ausschalten zu können, da meist auch die umliegenden Module betroffen sind. Die generelle Möglichkeit, Detektormodule einzeln abzuschalten, besteht durch den Control und Feedback Pfad.

#### Der Control und Feedback Pfad

Der Control und Feedback Pfad misst alle wichtigen Betriebsparameter, wie Spannungen, Ströme und Temperaturen des Detektors, die in Tabelle 3.1 genannt sind. Zusätzlich sind digitale Ausgänge zum Schalten von Detektor-Komponenten, wie z.B. einzelnen Detektor-Modulen oder des GBT, vorgesehen. Auf jedem Detektor-Modul wird sich im Pixeldetektor ein Temperatursensor befinden, so dass die kleinste Ausleseeinheit hier jeweils ein Detektor-Modul ist. Die Hochspannung wird direkt an der Versorgungseinheit im Kontrollraum gemessen, somit werden keine weiteren Leitungen im Detektor benötigt. Die Niederspannungen müssen je nach Konzept für die Detektorversorgung auf unterschiedliche Weise gemessen werden, die Konzepte hierzu werden im Folgenden noch genauer erläutert.

Um zusätzliche lange Leitungen im Detektor zu sparen, sollten Ströme und Temperaturen so nah wie möglich an den Modulen im Detektor gemessen werden. Dazu muss eine neuartige DCS-Komponente entwickelt werden, die drei wichtige Kriterien erfüllt: Die Komponente muss sehr leicht sein, zusätzlich aber auch strahlenhart, und sie sollte einen geringen Leistungsverbrauch haben. Diese Kriterien können nur durch einen speziellen, sehr kleinen Schaltkreis (ASIC, Chip) erfüllt werden, der im geeigneten Halbleiter-Prozess entwickelt wird. Das Chipdesign wurde in der Wuppertaler DCS-Gruppe bisher nicht durchgeführt, ist für das zukünftige Kontrollsystem aber unumgänglich und startet somit bei der Entwicklung des Control und Feedback Pfades.

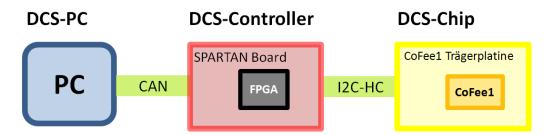

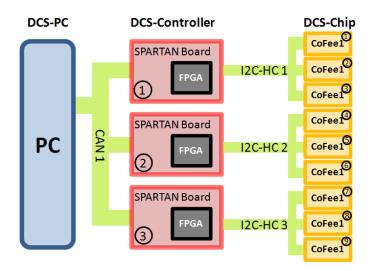

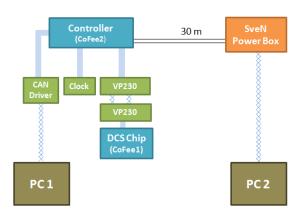

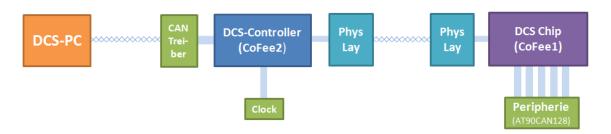

Für das zukünftige Kontrollsystem wird an zwei unterschiedlichen Chipdesigns entwickelt: dem DCS-Chip und dem DCS-Controller. Der DCS-Chip wird die DCS-Daten im Detektor messen und sie an den DCS-Controller senden, der die Daten von mehreren DCS-Chips bündelt und an die Ausleseelektronik im Kontrollraum weiter gibt. Umgekehrt werden die DCS-Befehle vom Kontrollraum über den DCS-Controller an die DCS-Chips gesendet. Die Übertragungsstrecke beträgt insgesamt etwa 100 m vom Detektor zum Kontrollraum, dabei wird sich der DCS-Controller ca.

20 m entfernt vom DCS-Chip befinden. Die in Abbildung 3.1 gezeigte Verbindung zwischen DCS-Chip und dem DCS-Controller steht stellvertretend für ein ganzes Netzwerk aus DCS-Controllern und DCS-Chips, welches in Kapitel 3.3 ausführlich beschrieben wird.

Um eine permanente Überwachung und Steuerung des Detektors für sämtliche Betriebszustände zu realisieren, muss der Control und Feedback Pfad jederzeit zuverlässig betriebsbereit sein. Das steht im Gegensatz zum Diagnostics-Pfad, der auf Abruf zusätzliche DCS-Informationen zur Verfügung stellt.

## Der Diagnostics-Pfad

Der grüne Pfad aus Abbildung 3.1 ist der Diagnostics-Pfad. Hier werden zusätzliche DCS-Informationen mit einer Auflösung pro FE-Chip über den optischen Datenstrom gesendet. Man erhält hier eine deutlich höhere Informationsdichte und braucht dabei im Detektor kein zusätzliches Material. Diese Methode ist ein weit verbreitetes Konzept für ein Detektorkontrollsystem. Der Nachteil hier ist allerdings, dass dieser Pfad nur betriebsbereit ist, wenn der komplette Detektor lauffähig ist, also der optische Datenpfad funktioniert.

Der Diagnostics-Pfad liefert Informationen über Spannungen, Ströme und Temperaturen. Die Elektronik zur Messung dieser Parameter wird im Front-End-Chip enthalten sein.

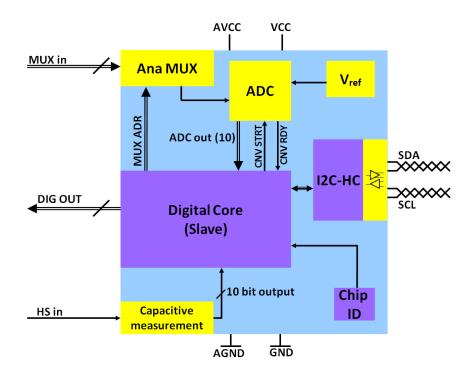

# 3.2.1 Der DCS-Chip

Der DCS-Chip wird sich auf der EoS-Karte befinden, die jeweils zwei Versorgungseinheiten bedienen kann. Es wird im Weiteren von der seriellen Detektorversorgung ausgegangen, da diese sehr wahrscheinlich für den Pixeldetektor verwendet werden wird. Somit werden jeweils acht Detektormodule eine Versorgungseinheit bilden, was sich in der Zahl der Ein- und Ausgänge des DCS-Chips wiederfindet.

Pro Versorgungseinheit wird es einen oder mehrere GBTs geben, so dass ein DCS-Chip mehrere GBTs schalten kann. Mit dem DCS-Chip wird es möglich sein, den GBT in einen Niedrigverbrauchsmodus zu versetzen.

Für das Ein- und Ausschalten von einzelnen Detektormodulen in einer seriell versorgten Kette sind verschiedene Ansätze vorhanden. Der Befehl zum Schalten der Detektormodule soll grundsätzlich vom DCS kommen, ob der DCS-Chip dafür verantwortlich sein wird oder diese Befehle separat geführt werden, ist noch nicht geklärt. Ein Ansatz für die Lösung dieses Problems ist in Kapitel 3.2.2 gezeigt.

Der DCS-Chip wird voraussichtlich 42 Ein- und Ausgänge erhalten. Darunter sind die Leitungen zur Temperatur- und Spannungsmessung von  $2 \times 8$  Detektormodulen, zur Feuchtemessung sowie zur Überwachung und Steuerung der EoS-Karte enthal-

ten. Eine genaue Aufstellung der Ein- und Ausgänge des DCS-Chips ist in Tabelle 3.2 zu finden.

| Zahl der Anschlüsse | Messung oder Steuerung von                         |

|---------------------|----------------------------------------------------|

| 18                  | Temperaturmessung der Detektormodule,              |

|                     | je 8 NTCs teilen sich 1 Return-Leitung             |

| 16                  | Niederspannungen per Spannungsteiler               |

| 1                   | kapazitiver Feuchtesensor                          |

| 1                   | Referenzkapazität für die Feuchtemessung           |

| 2                   | Temperaturmessung der EoS-Karte                    |

| 2                   | Niederspannung der EoS-Karte                       |

| 4                   | digitale Ausgänge (2 pro GBT) zum Schalten des GBT |

| Summe = 44          |                                                    |

Tabelle 3.2: Detaillierte Aufstellung der Ein- und Ausgänge des DCS-Chips

Abbildung 3.2: Schema des DCS-Chips. In gelb sind die analogen, in violett die digitalen Komponenten des DCS-Chips gezeigt. [15]

In Abbildung 3.2 ist das Blockdiagramm des DCS-Chips gezeigt. Die analogen Komponenten sind dabei gelb dargestellt. Unter ihnen befinden sich ein analoger Multiplexer und ein Analog-Digital-Konverter (= ADC) mit 10-Bit Auflösung zur Messung der Temperaturen und Niederspannungen der Detektormodule sowie eine Referenzspannungsquelle für den ADC. Für die kapazitive Feuchtigkeitsmessung werden

sich Schmitt-Trigger und Rückkopplungswiderstände im DCS-Chip befinden ("Capacitive measurement"). Der Feuchtesensor und ein Referenzkondensator werden im Detektorvolumen platziert.

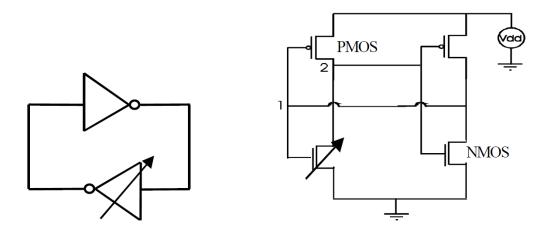

Der in violett dargestellte Digitalteil des DCS-Chips beinhaltet den Slave für das Master-Slave-Protokoll I2C-HC, auf welches in Kapitel 5 noch genauer eingegangen wird.

Der Slave erhält die Lese- bzw. Schreibbefehle vom DCS-Controller und führt den gewünschten DCS-Befehl aus. Zur digitalen I2C-HC-Schnittstelle gehört auch eine analoge Komponente, die die Signale für Daten und Clock auf einen differentiellen Bus treibt. Zusätzlich wird jeder DCS-Chip eine Chip-ID zur einfacheren Identifikation erhalten.

Die Funktion des DCS-Chips ist nun im Detail bekannt. Im Folgenden kann somit auf den Einsatz des DCS-Chips im Detektor eingegangen werden.

# 3.2.2 DCS-Konzepte für zwei unterschiedliche Ansätze der Detektorversorgung

Da bisher noch nicht klar ist, ob die serielle oder die parallele Detektorversorgung verwendet wird, gibt es zwei unterschiedliche Konzepte für die Anbindung des DCS-Chips an die Detektor-Komponenten.

#### DCS für die parallele Versorgung des Detektors

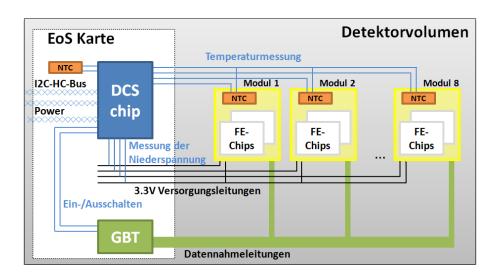

In Abbildung 3.3 ist das DCS für die parallele Detektorversorgung gezeigt. Zu sehen ist der auf der EoS-Karte lokalisierte DCS-Chip mit den Verbindungen zu einer Ausleseeinheit von 8 Detektormodulen. Der DCS-Chip wird zwei Ausleseeinheiten steuern und kontrollieren können, zur einfacheren Übersicht wurde auf der schematischen Zeichnung nur eine Ausleseeinheit eingezeichnet. Auch Leitungen für die von außen zugeführte Hochspannung, die das DCS direkt an den Versorgungseinheiten im Kontrollraum messen wird, sind nicht eingezeichnet worden.

Die Leitungen für die Niederspannungsversorgung verlaufen über die EoS-Karte. Deshalb kann mit dem DCS-Chip die Niederspannung pro Detektormodul durch sehr kurze Leitungen auf der EoS-Karte abgegriffen werden. Es sind keine zusätzlichen Leitungen zum Detektormodul notwendig.

Auf jedem Detektormodul wird sich ein NTC zur Temperaturmessung befinden. Zur Auslese der Temperatursensoren werden (n+1) Leitungen benötigt, wenn n Detektormodule vorhanden sind. Die Sensoren teilen sich dabei eine gemeinsame Return-Leitung. Die voraussichtlich 9 Leitungen pro Ausleseeinheit werden nur zwischen Detektormodul und DCS-Chip benötigt und können sehr dünn sein, da es reine Messleitungen sind. Ein weiterer Temperatursensor wird sich auf der EoS-Karte oder

Abbildung 3.3: Das DCS für die parallele Versorgung des Pixeldetektors, wobei nur eine Ausleseeinheit eingezeichnet ist.

der Kühlstruktur befinden. Auch diesen wird der DCS-Chip durch kurze Leitungen auf der EoS-Karte auslesen können.

Auf der EoS-Karte befindet sich auch der GBT. Voraussichtlich wird dieser vom DCS-Chip gesteuert werden können. Der DCS-Chip kann den GBT zurücksetzen bzw. ein- und ausschalten oder ihn in einem Stromsparmodus starten, in dem der GBT auch bei verringerter Detektor-Kühlung betrieben werden kann.

Der DCS-Chip ermöglicht also die Spannungs- und Temperaturmessung pro Detektormodul sowie die Steuerung des GBT. Dazu werden für dieses Detektor-Konzept insgesamt (n+1) Leitungen im Detektorvolumen benötigt.

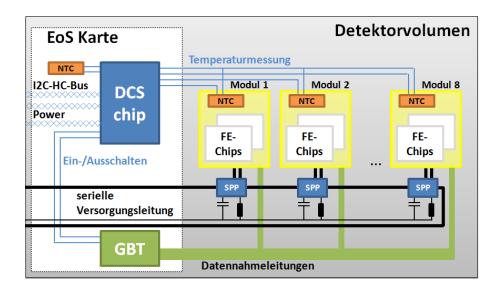

#### DCS für die serielle Versorgung des Detektors

Das Konzept der seriellen Detektorversorgung reduziert die Leitungszahl im Detektorvolumen sehr stark. Ein auftretendes Problem bei diesem Ansatz der Detektorversorgung ist die Frage, wie Detektormodule einzeln ausgeschaltet werden können, ohne dem Detektor zusätzliche Leitungen zuzufügen. Es wird also ein Überbrückungsmechanismus benötigt, der einzelne Module einer seriell versorgten Kette abschalten kann.

Solch ein Mechanismus ist dringend notwendig, da ein zu stark rauschendes Detektormodul vom Bus genommen werden muss, damit die Daten der anderen Module nicht verloren gehen. Durch eine Neukalibration kann ein solches Detektormodul nach einem kurzen Stop der Datennahme eventuell wieder mit in die Auslese aufgenommen werden, dafür sollte der Überbrückungsmechanismus einfach und flexibel steuerbar sein. Für die Überwachung und Steuerung bietet sich der DCS-Chip an,

Abbildung 3.4: Das DCS für die serielle Detektorversorgung, schematisch dargestellt anhand einer Versorgungseinheit. Die Messung der Spannungen der Module vom DCS-Chip ist nicht eingezeichnet, da hierfür die genaue Methode noch bestimmt werden muss. [12]

da dieser durch kurze Leitungen auf der EoS-Karte diese Aufgaben übernehmen könnte.

Momentan ist für den Überbrückungsmechanismus der Serial-Powering-Protection-Chip (= SPP-Chip) angedacht, der über einen 1-Draht-Bus versorgt und gesteuert werden können soll. Inwiefern dieser Chip wirklich für die Überbrückung einzelner Pixelmodule in Frage kommt, wird momentan in verschiedenen Aufbauten getestet, da der SPP-Chip für den Streifen-Detektor entwickelt wurde und für den Pixeldetektor größere Ströme schalten muss.

Zwischen den einzelnen Detektormodulen herrschen durch die serielle Stromversorgung unterschiedliche Spannungsniveaus. Sollte der DCS-Chip die Niederspannung mit separaten Leitungen direkt an den Detektormodulen messen, so würde ein Spannungsteiler zusätzlich auf der EoS-Karte benötigt, um die Eingänge des DCS-Chips zu schützen. Um eine größere Materialersparnis zu erzielen, sollten auch andere Konzepte zur Messung der Niederspannung in Betracht gezogen werden. Dazu sind im Folgenden drei Konzepte vorgestellt, zu denen jeweils weitere Studien durchgeführt werden müssen:

- 1. Die Niederspannung könnte über die HV-Return-Leitung gemessen werden. Bisher ist allerdings noch keine HV-Return-Leitung konkret geplant worden.

- 2. Ein weiterer möglicher Kandidat zur Messung der Niederspannung wäre die Low Voltage Differential Signal (= LVDS) Datenleitung zwischen FE-Chip und GBT. Dazu müsste die Spannungsmessung vom FE-Chip durchgeführt

werden. Im momentanen FE-Chip sind bisher keine Entwicklungen in diese Richtung geplant.

3. Die wahrscheinlichste Möglichkeit eine Information über die Modulspannungen ohne zusätzliche Leitungen zu erhalten, wäre die Bestimmung der Spannung über die Einschaltreihenfolge durch den SPP-Chip. Dabei würde beim Einschalten der Detektormodule jeweils die Spannungsdifferenz nach jedem eingeschalteten Modul direkt an der Stromquelle messbar sein. Diese Niederspannung könnte einmal beim Einschalten der Detektormodule gemessen, während des Betriebs allerdings nicht mehr aktualisiert werden.

Aus der obigen Aufzählung wird schnell klar, dass dringend ausführliche Studien für die Messung der Niederspannung notwendig sind, wenn das Detektorsystem konkreter bekannt ist.

Wie auch für die parallele Detektorversorgung werden für die serielle Versorgung (n+1) Leitungen für n Detektormodule zur Temperaturmessung benötigt, sowie kurze Leitungen auf der EoS-Karte zur Auslese eines zusätzlichen Temperatursensors. Der DCS-Chip wird auch für dieses Konzept den GBT ein- bzw. ausschalten oder ihn in einen Stromsparmodus versetzen können.

#### 3.3 Der DCS-Controller-Chip

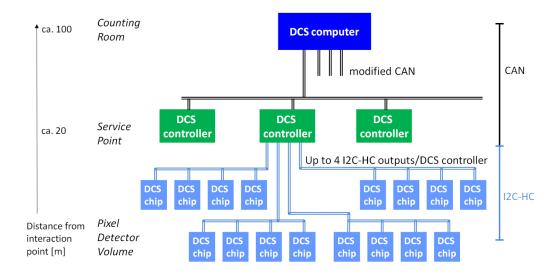

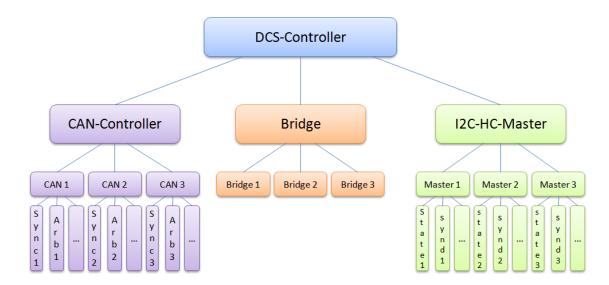

Das Netzwerk aus DCS-Controller und DCS-Chip bildet die zentrale Einheit des Detektorkontrollsystems.

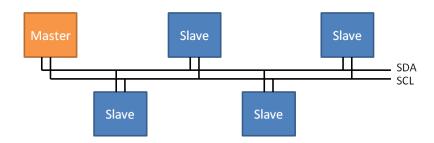

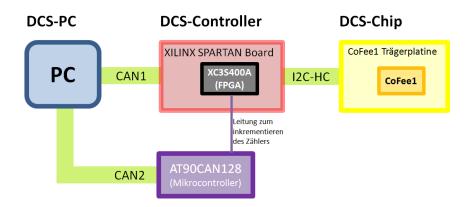

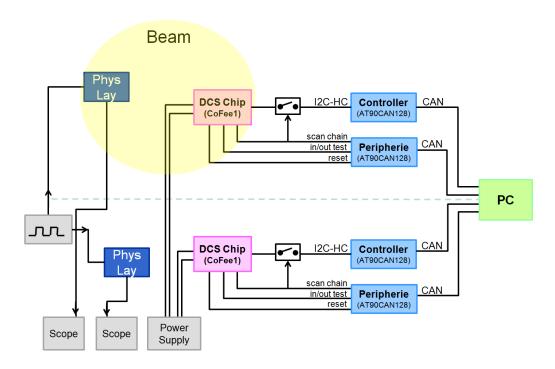

Der DCS-Controller ist dafür zuständig, die Daten von bis zu 16 DCS-Chips zusammenzufassen und sie an den Kontrollraum weiterzugeben. Umgekehrt empfängt der DCS-Controller Befehle vom Kontrollraum und sendet diese an die DCS-Chips. Dabei muss die Datenübertragung in der Strahlungsumgebung absolut fehlerfrei sein. Für die Gewährleistung einer fehlerfreien Übertragung muss das Netzwerk eine Balance zwischen Redundanz der Komponenten und Minimierung der Strahlungslänge herstellen. Aus diesem Grund werden an jeden DCS-Controller vier Busse angeschlossen sein, an denen sich jeweils bis zu vier DCS-Chips befinden werden.

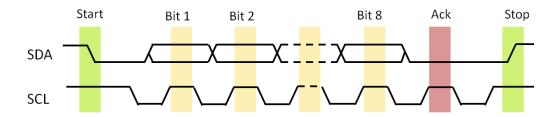

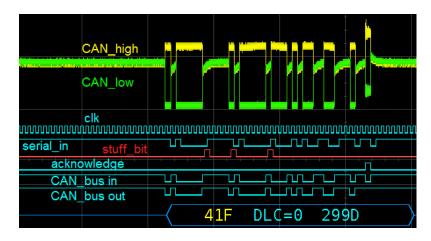

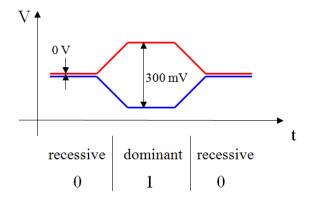

Das DCS-Netzwerk ist in Abbildung 3.5 gezeigt. Zu sehen ist auch, dass für die Kommunikation vom DCS-Controller zum DCS-Chip ein anderes Protokoll verwendet wird als für die Kommunikation zum Kontrollraum. Das CAN-Protokoll hat eine ausgeprägte Fehlererkennung und kann mit nur zwei Leitungen (twisted pair) Daten über lange Strecken sicher übertragen. Das für die Kommunikation zum Detektor verwendete I2C-HC-Protokoll ist ein einfach-selbstkorrigierendes Protokoll, welches in der hohen Strahlungsumgebung im Pixeldetektor eine verlustfreie, sichere Kommunikation ermöglicht. Auf den Aufbau und die Funktion der Protokolle wird in Kapitel 5 noch genauer eingegangen.

Abbildung 3.5: Das DCS-Netzwerk

Einer der Gründe für den DCS-Controller ist die begrenzte Reichweite der I2C-HC-Kommunikation. Tests zur Bestimmung der Reichweite werden in Kapitel 7.3 dargestellt. Die CAN-Datenübertragung dagegen ist dazu geeignet, für die angestrebten CAN-Bitraten von 250 kHz über eine Distanz von minimal 80 m fehlerfrei zu kommunizieren.

Ein weiterer Grund für einen DCS-Controller ist, dass dieser dazu beiträgt, die Zahl der DCS-Leitungen im Detektorvolumen zu reduzieren. Der zukünftige Pixeldetektor wird eine dreifache Zahl an Pixelzellen verglichen mit dem gegenwärtigen Pixeldetektor haben. Die zur Verfügung stehenden räumlichen Gegebenheiten werden sich dabei allerdings nicht vergrößern. Es sollte also maximal dieselbe Anzahl an Leitungen wie beim jetzigen Detektor aus dem Pixeldetektor herausgeführt werden.

Der DCS-Controller wird bewusst an einer Stelle im Detektor eingebaut, die im Notfall zugänglich ist. Während Komponenten auf der EoS-Karte nach dem Einbau nicht mehr nachträglich repariert werden können, ist das für den 20 m entfernten Service Point schon eher möglich, an dem sich der DCS-Controller befinden wird.

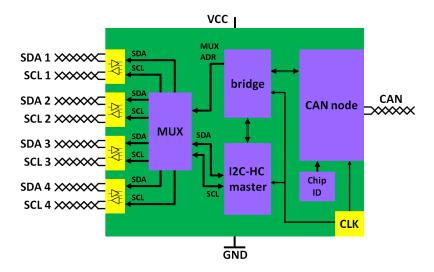

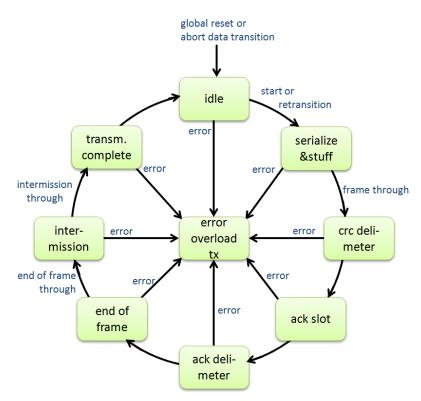

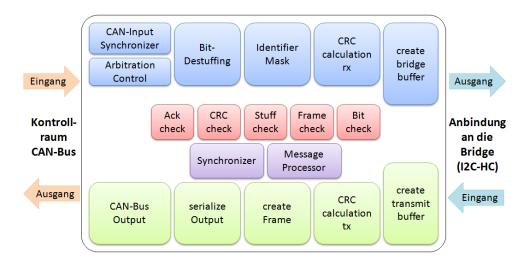

In Abbildung 3.6 ist der DCS-Controller schematisch dargestellt. Dabei sind die digitalen Komponenten in violett und die analogen Komponenten in gelb markiert. Die rechte Seite der Abbildung 3.6 stellt die Anbindung zum Kontrollraum über einen CAN-Bus dar. Der CAN-Knoten beinhaltet das Standard CAN-Protokoll<sup>3)</sup> nach den Bosch-Spezifikationen [16]. Die DCS-Befehle werden dort entgegengenommen. In der "bridge" werden die DCS-Befehle in das I2C-HC-Protokoll übersetzt und dann mit dem I2C-HC-Master über einen Multiplexer auf einen der vier I2C-HC-Busse zum DCS-Chip im Detektor gesendet. Umgekehrt kann der DCS-Controller

$<sup>^{3)}</sup>$ Version A

Abbildung 3.6: Schematische Darstellung des DCS-Controllers. In violett sind die digitalen, in gelb die analogen Komponenten dargestellt [15].

die zurückgelesenen Daten des DCS-Chips vom I2C-HC-Master in der bridge für das CAN-Protokoll übersetzen und dann auf dem CAN-Bus zum Kontrollraum senden.

So wie die DCS-Chips wird auch jeder DCS-Controller eine eigene Chip-ID erhalten. Damit ist die eindeutige Identifikation der Komponenten möglich, was für die Kommunikation im DCS-Netzwerk wichtig ist.

### 3.4 Vergleich der Leitungsanzahl des momentanen und des zukünftigen DCS

Das zukünftige Detektorkontrollsystem wurde unter dem Aspekt der größtmöglichen Sicherheit, aber auch der maximalen Materialreduktion entwickelt. Vor allem die Einschränkung, dass sich zwar die Zahl der Auslesekanäle des Detektors vergrößert, aber der Platz für Versorgungsleitungen derselbe bleibt, muss bei solch einem Design berücksichtigt werden. Im Folgenden soll gezeigt werden, dass das DCS-System für das HL-LHC Upgrade trotz einer höheren Zahl der Auslesekanäle insgesamt weniger Leitungen benötigt. Die Angaben für die Leitungszahlen des zukünftigen Pixeldetektors beruhen auf der in Kapitel 2.6 beschrieben Modularität. Für die Detektorversorgung wird bei der folgenden Berechnung vom Konzept der seriellen Detektorversorgung ausgegangen.

Der zukünftige Pixeldetektor wird insgesamt 3833 Module haben, wobei diese Zahl alle Module (ob 2-fach, 4-fach oder 6-fach Module) umfasst. Diese Module werden in Versorgungseinheiten unterteilt, die jeweils 8 Module beinhalten. Es wird insgesamt 716 Versorgungseinheiten geben. Da in den innersten beiden Lagen mehrere

Versorgungseinheiten von einer EoS-Karte aus versorgt werden, ist die Gesamtzahl der EoS-Karten mit 684 etwas geringer als die der Versorgungseinheiten.

Pro Versorgungseinheit wird ein DCS-Chip benötigt, so dass im gesamten DCS insgesamt 716 DCS-Chips eingesetzt werden. Die Zahl der DCS-Controller steht noch nicht fest. Es werden aber maximal 16 DCS-Chips und minimal 8 DCS-Chips von einem DCS-Controller im DCS-Netzwerk angesteuert. Somit werden zwischen 45 und 90 DCS-Controller zum Einsatz kommen.

Der momentane Pixeldetekor hat insgesamt 1744 Detektormodule, etwa die Hälfte der zukünftigen Auslesekanäle. Für den momentanen Detektor wird die Kabelzahl immer pro Detektormodul berechnet.

| Pixeldetektor DCS | Kabelpaare   | Kabelpaare     | Kabelpaare     |  |

|-------------------|--------------|----------------|----------------|--|

|                   | Hochspannung | Niederspannung | für DCS        |  |

| aktuell           | 1744         | 3548           | 5232           |  |

| für HL-LHC        | 1432         | 716 + 684*     | $2832 + 684^*$ |  |

Tabelle 3.3: Gegenüberstellung der Leitungsanzahl für das gegenwärtige und das zukünftige DCS für das HL-LHC Upgrade. Die mit \* markierten Zahlen sind Kabelpaare, die nur bis zur EoS-Karte geführt werden.

Für die Versorgung des Detektors mit Hochspannung wird für das momentane DCS ein Kabelpaar pro Modul benötigt. Für das zukünftige DCS werden aufgrund der seriellen Detektorversorgung pro Versorgungseinheit 2 Kabelpaare benötigt, das entspricht einem Kabelpaar pro 4 Detektormodulen. Die Gesamtzahl der Hochspannungsleitungen ist für das zukünftige DCS geringer als für das momentane, was auch in Tabelle 3.3 gezeigt ist.

Im momentanen Pixeldetektor werden pro Modul 2 Niederspannungs-Kabelpaare benötigt. Das entspricht einer Summe von 3548 Kabelpaaren. Für das zukünftige Layout, in dem drei verschiedene Modulsorten (zweifach, vierfach, sechsfach) vorgesehen sind, wird pro Versorgungseinheit ein Kabelpaar benötigt. Das entspricht insgesamt 716 Leitungen, wie in Tabelle 3.3 zu sehen ist. Die Zahlen für das momentane und das zukünftige DCS sind jedoch nicht direkt vergleichbar, da für die vierfach und die sechsfach Module ein höherer Stromverbrauch durch eine größere Zahl an FE-Chips besteht. Dementsprechend haben die Kabel ein größeres Volumen. Rechnet man dieses um auf die momentan verwendeten Niederspannungskabel, so würden statt der 716 Leitungspaare aus Tabelle 3.3 3088 Kabelpaare benötigt, was unterhalb der Zahl der Leitungen des momentanen Pixeldetektors liegt. Für die Versorgung der EoS-Karte kommt noch ein weiteres Kabelpaar pro EoS-Karte hinzu, also 684 Kabelpaare. Diese Kabelpaare werden nur bis zu den Staveenden geführt und müssen somit separat betrachtet werden.

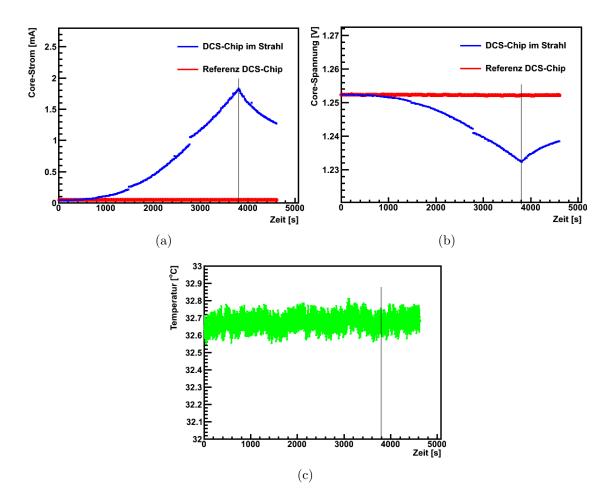

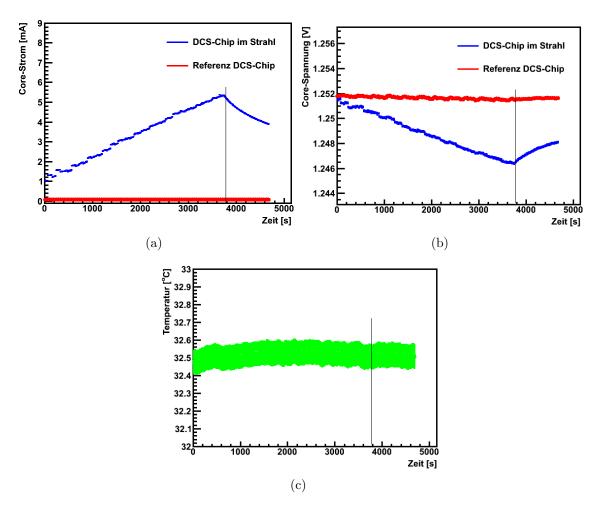

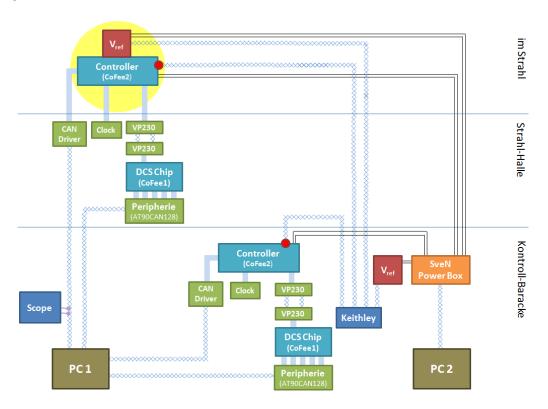

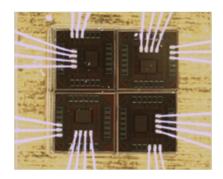

Für das DCS werden im aktuellen Pixeldetektor pro Modul jeweils 3 Kabelpaare benötigt. Diese Leitungen sind sehr dünn, da für die beiden Niederspannungen zwei